然而�,隨著DDR工作頻率提高,DDR PHY訓(xùn)練的準(zhǔn)確性和精度要求也隨之提高���。訓(xùn)練的準(zhǔn)確性和精度決定了DDR系統(tǒng)能否穩(wěn)定可靠地工作在較高的頻率�����。

DDR PHY訓(xùn)練所面臨的挑戰(zhàn)

DDR訓(xùn)練的種類繁多���,每個(gè)訓(xùn)練的結(jié)果都不能出錯(cuò)。同時(shí)固態(tài)技術(shù)協(xié)會(huì)定義的訓(xùn)練序列都比較單一���,如果只使用這些默認(rèn)序列的話�,訓(xùn)練結(jié)果在實(shí)際工作中并不是一個(gè)最優(yōu)值���。

目前絕大多數(shù)DDR PHY都采用硬件訓(xùn)練的方式�,如果硬件算法有問(wèn)題���,會(huì)導(dǎo)致訓(xùn)練出錯(cuò)���,DDR無(wú)法正常穩(wěn)定地工作�����,導(dǎo)致整個(gè)SoC的失敗��。同時(shí)����,硬件訓(xùn)練模式很難支持復(fù)雜的訓(xùn)練序列和訓(xùn)練算法���,從而無(wú)法得到訓(xùn)練結(jié)果的最優(yōu)解��。

芯耀輝的DDR PHY采用軟硬件結(jié)合的固件(firmware)訓(xùn)練方式跳出了上述DDR PHY訓(xùn)練模式的固定思維����。

芯耀輝DDR PHY在訓(xùn)練上的優(yōu)勢(shì)

解決寫(xiě)入均衡(write leveling)的難題

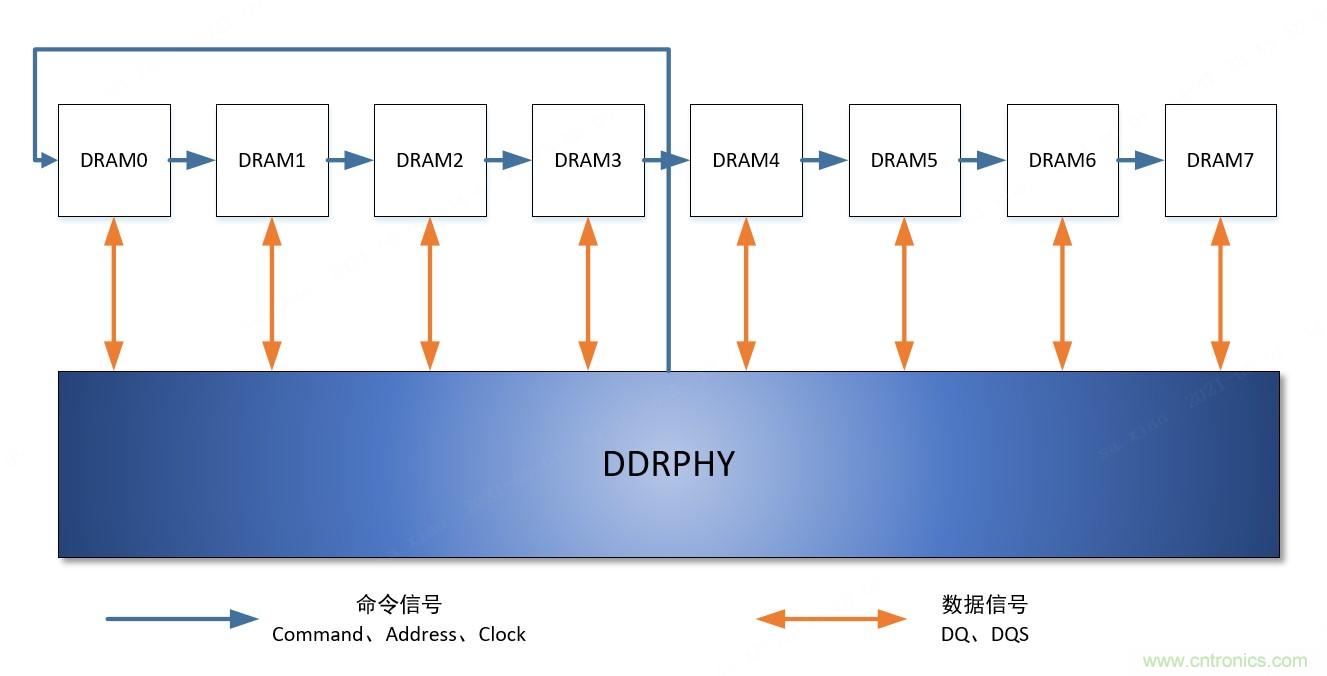

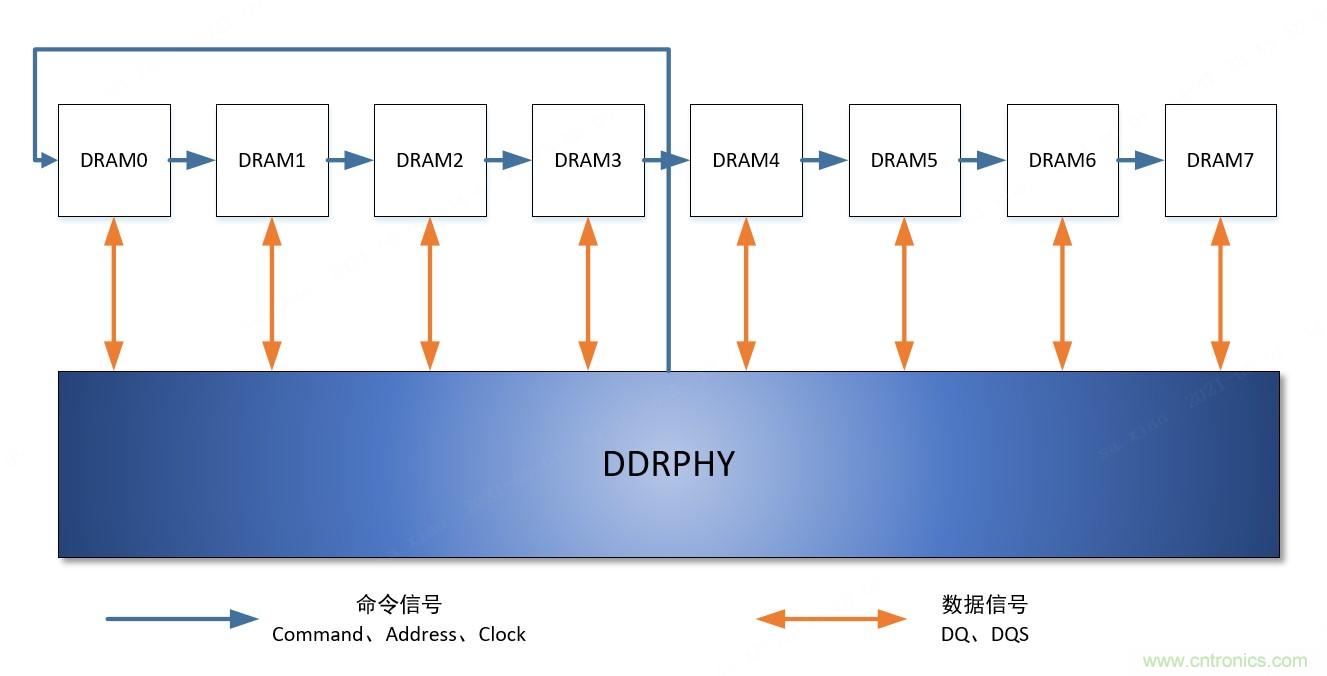

寫(xiě)入均衡是為了計(jì)算出flyby結(jié)構(gòu)下命令通路和數(shù)據(jù)通路的走線延遲的差值�,在DDR PHY中把這個(gè)差值補(bǔ)償?shù)綌?shù)據(jù)通路上,從而最終讓數(shù)據(jù)通路和命令通路的延遲達(dá)到一致��。

圖2:DDR flyby拓?fù)浣Y(jié)構(gòu)示意圖

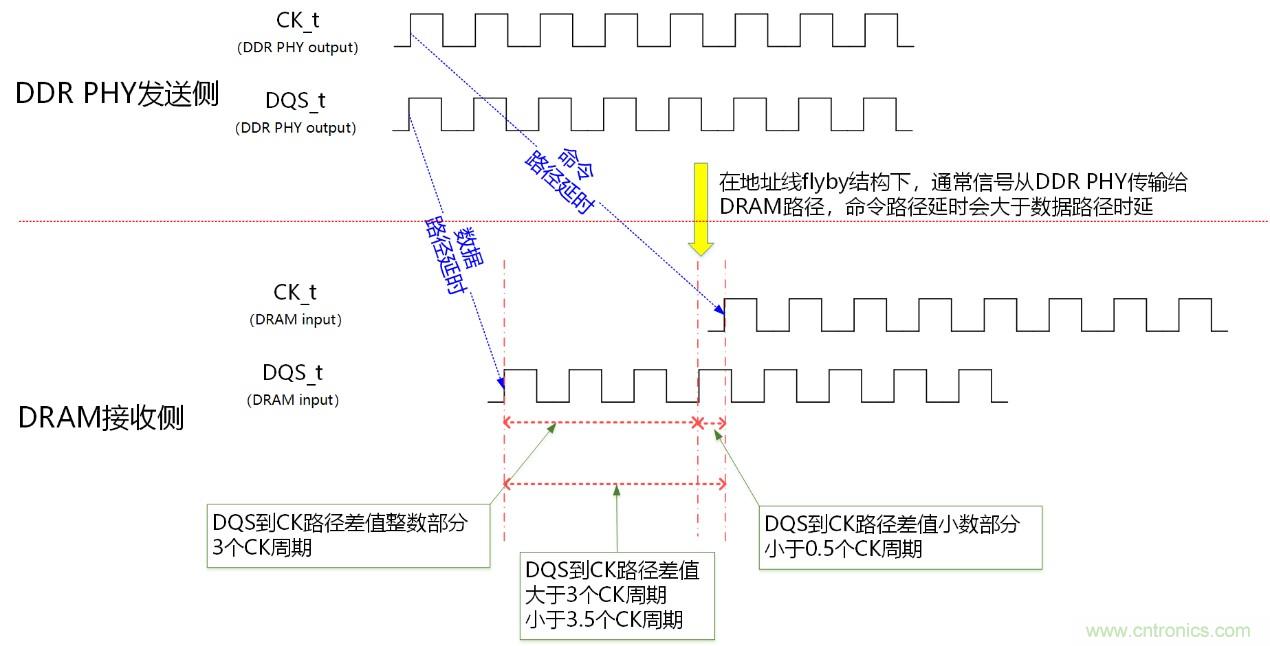

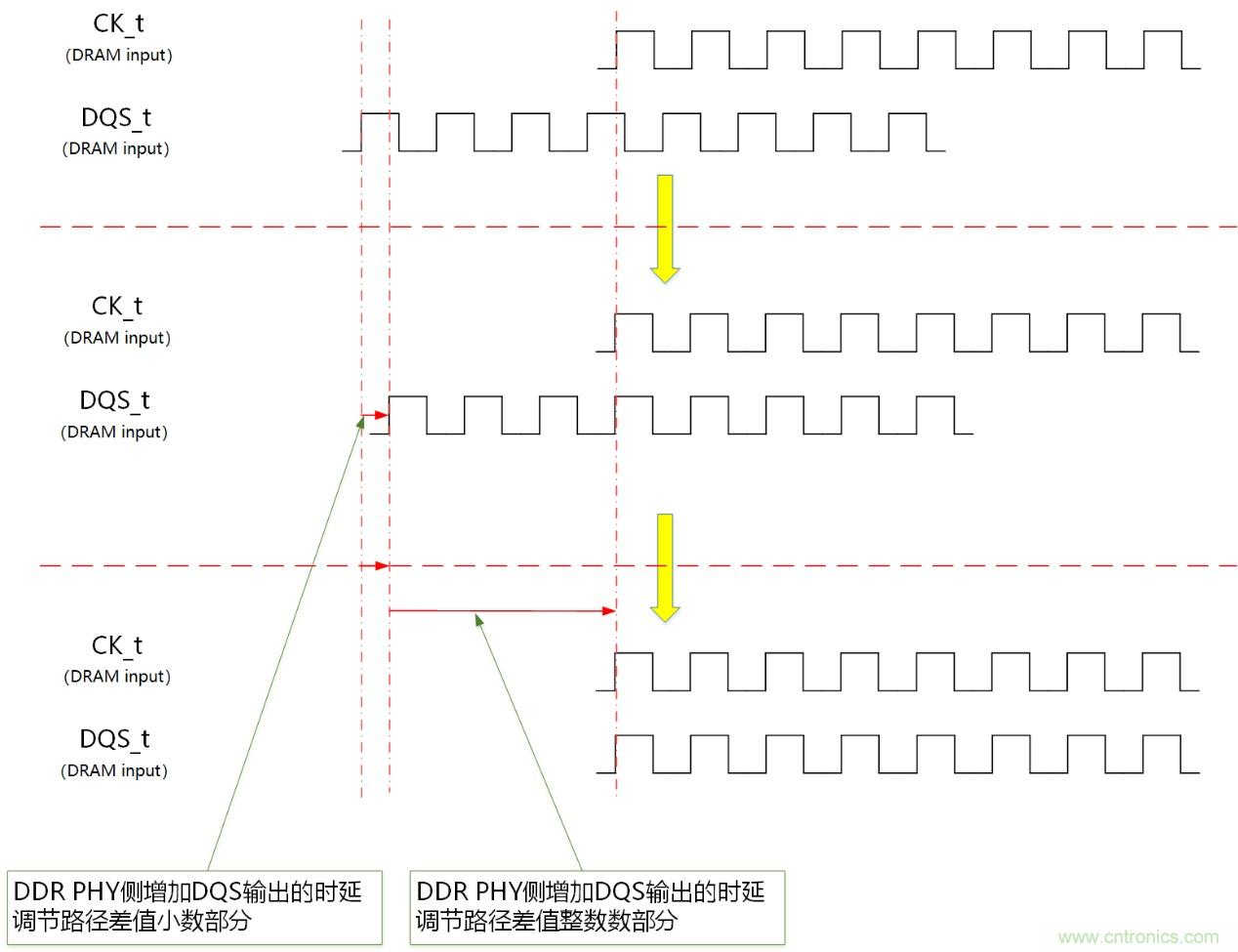

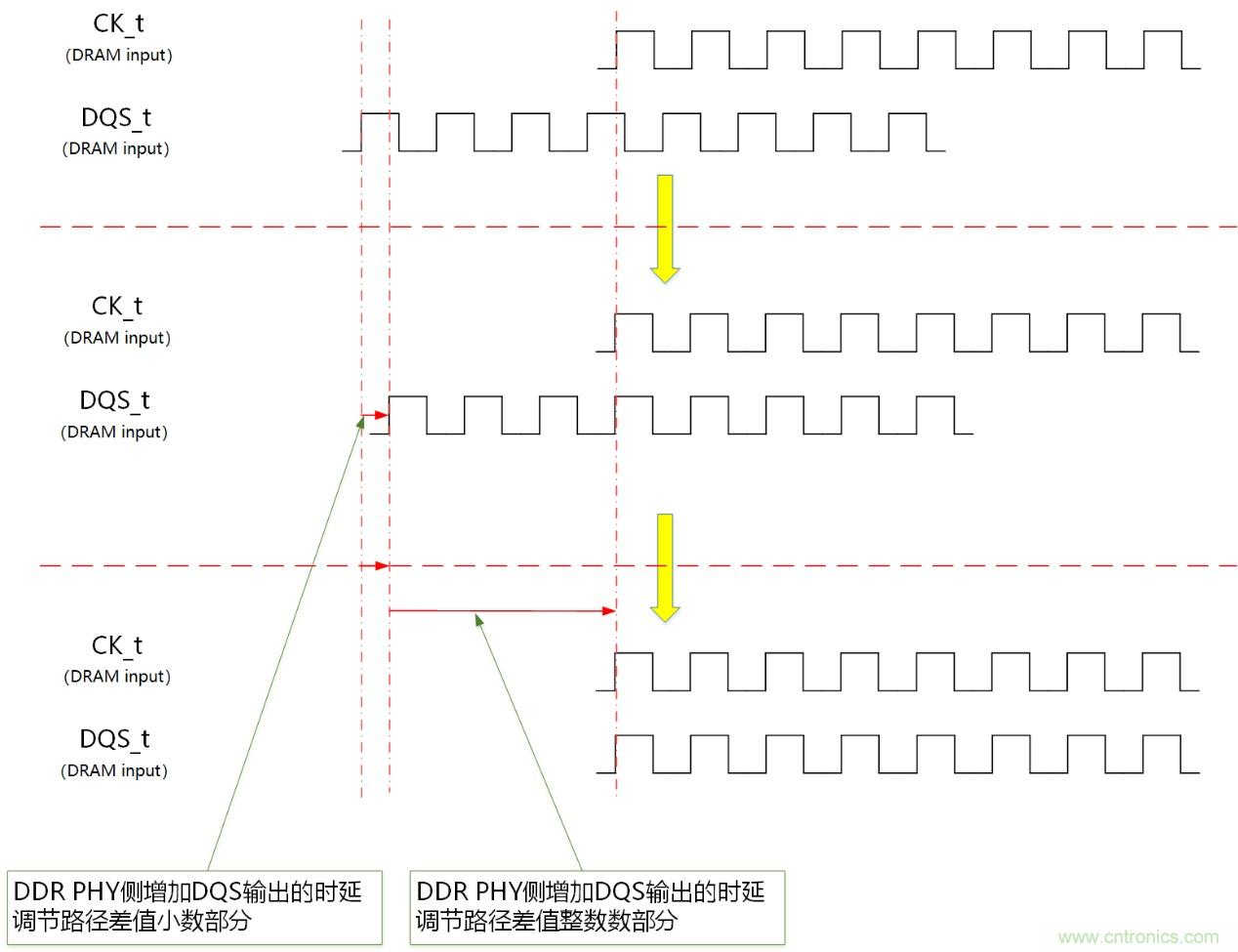

在實(shí)際的應(yīng)用中���,命令(command)路徑上的延時(shí)會(huì)超過(guò)數(shù)據(jù)(DQ)路徑的延時(shí)�����。假設(shè)路徑差值 = 命令路徑延時(shí) – 數(shù)據(jù)路徑延時(shí)���,一般路徑差值在0~5個(gè)時(shí)鐘周期之間?�?梢园崖窂讲钪捣譃檎麛?shù)部分和小數(shù)部分(單位是0.5個(gè)時(shí)鐘周期)��。

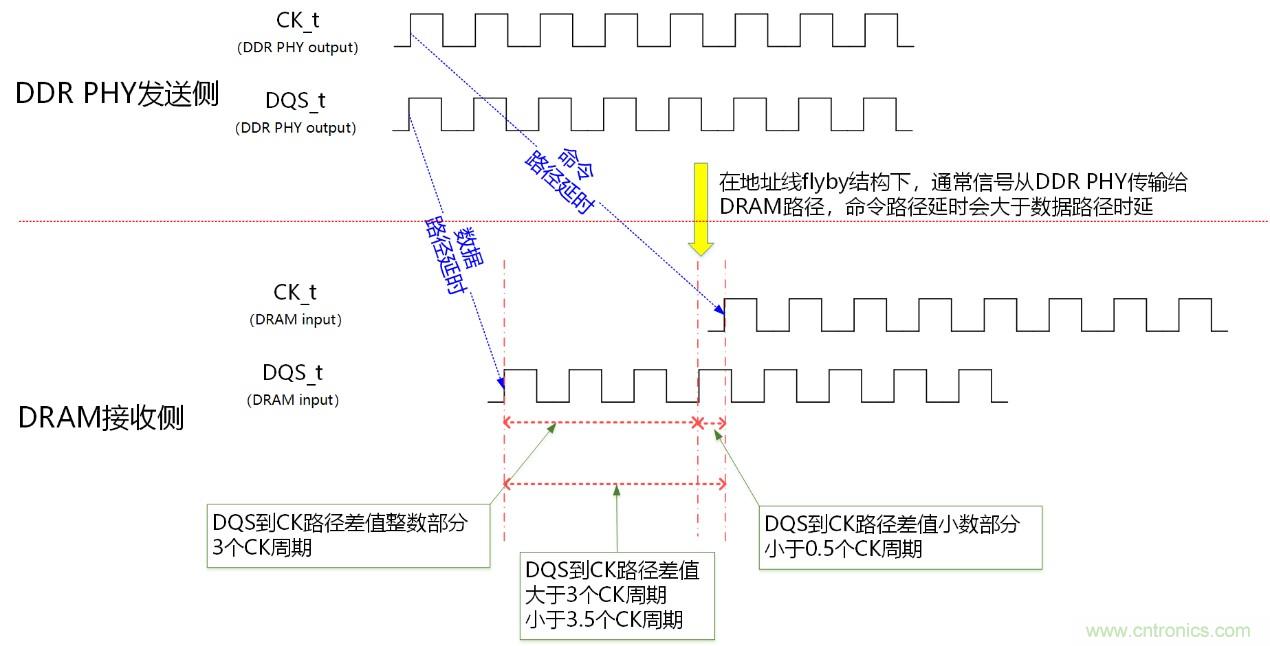

圖3:命令路徑延時(shí)�����、數(shù)據(jù)路徑延時(shí)和路徑差值

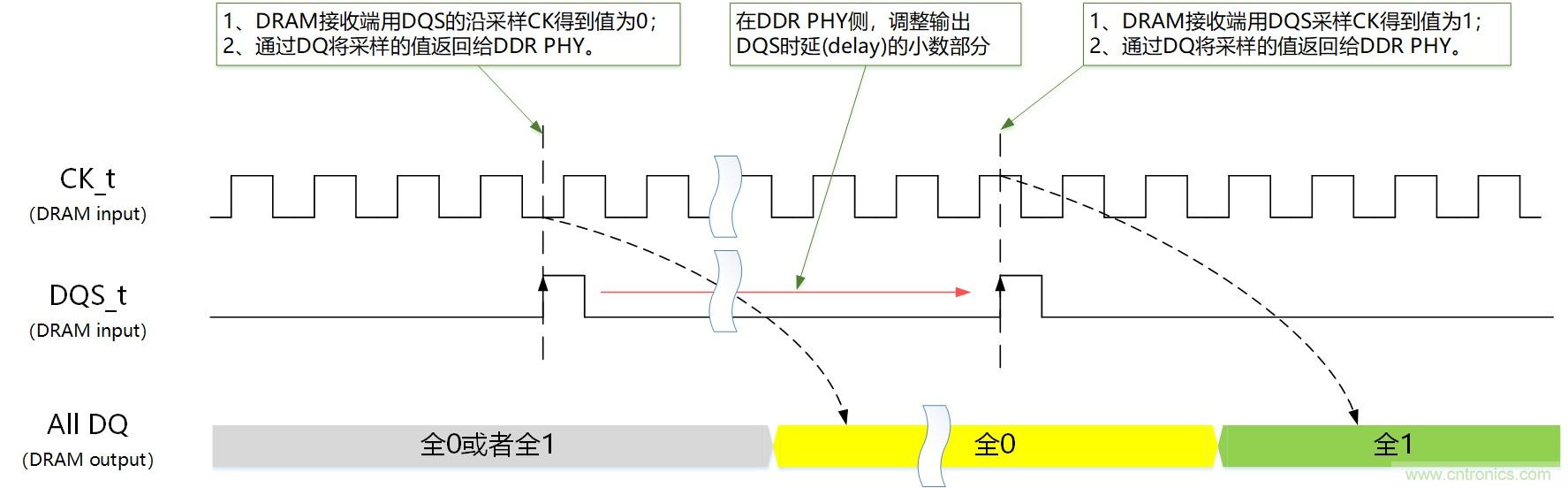

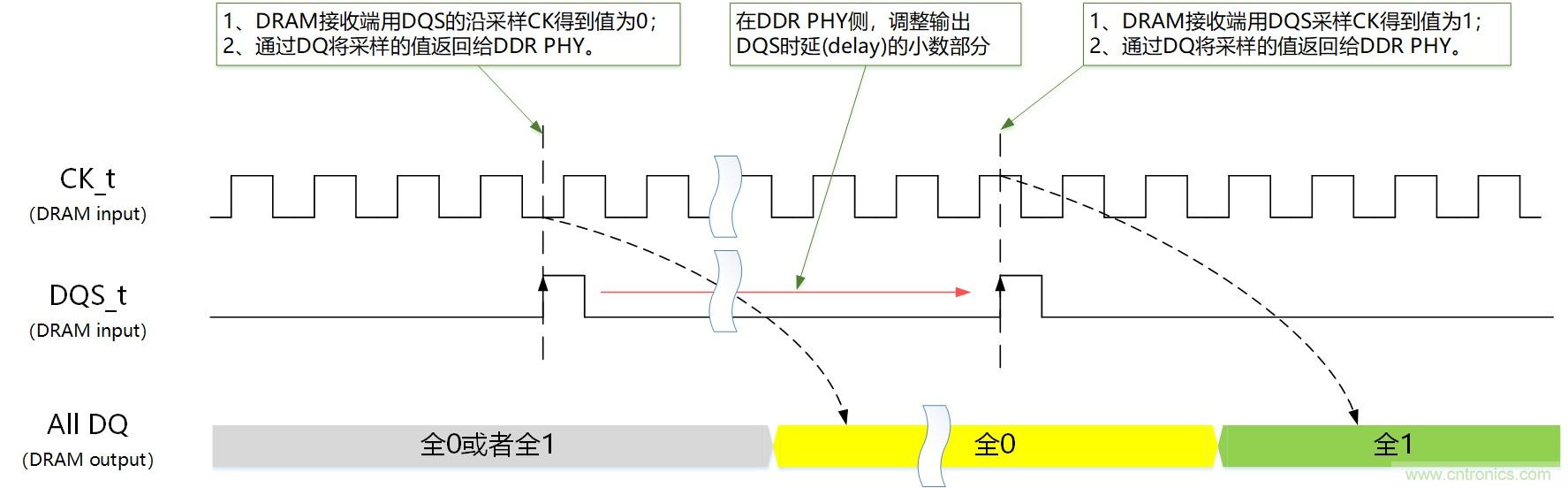

根據(jù)固態(tài)技術(shù)協(xié)會(huì)標(biāo)準(zhǔn)(如JESD79-4C)的寫(xiě)入均衡的要求����,DRAM在寫(xiě)入均衡模式下會(huì)用DDR PHY發(fā)送過(guò)來(lái)的DQS沿去采樣CK,并把采樣的值通過(guò)DQ返回給DDR PHY�。

圖4:寫(xiě)入均衡模式下調(diào)整DQS時(shí)延的示意圖

通過(guò)該訓(xùn)練,DDR PHY可以計(jì)算出命令與數(shù)據(jù)路徑延時(shí)差值的小數(shù)部分����,卻沒(méi)有辦法訓(xùn)練出命令與數(shù)據(jù)路徑延時(shí)差值的整數(shù)部分(把DQS多延遲一個(gè)時(shí)鐘周期或者少延遲一個(gè)時(shí)鐘周期,用DQS采樣CK的采樣值是相同的)��。

為了解決這個(gè)問(wèn)題,通常會(huì)根據(jù)版圖設(shè)計(jì)估算出大概的路徑差值�,從而自行得到路徑差值的整數(shù)部分,直接配置到DDR PHY的寄存器中�����。這種做法在頻率比較低��、量產(chǎn)一致性比較好的時(shí)候問(wèn)題不大����。但在大規(guī)模量產(chǎn)的時(shí)候,如果平臺(tái)之間的不一致性超過(guò)一個(gè)時(shí)鐘周期(LPDDR4最高頻下周期為468ps)的話�,上述直接配置整數(shù)部分的方法就沒(méi)法進(jìn)行工作了,必然會(huì)導(dǎo)致部分芯片無(wú)法正常工作�����。

芯耀輝采用固件的訓(xùn)練方式�,通過(guò)DDR寫(xiě)操作時(shí)特殊調(diào)節(jié)方法,能夠幫助客戶計(jì)算出路徑差值整數(shù)加小數(shù)部分��,無(wú)需客戶根據(jù)版圖設(shè)計(jì)估算路徑差值范圍��。

圖5:路徑差值整數(shù)部分訓(xùn)練和小數(shù)部分訓(xùn)練

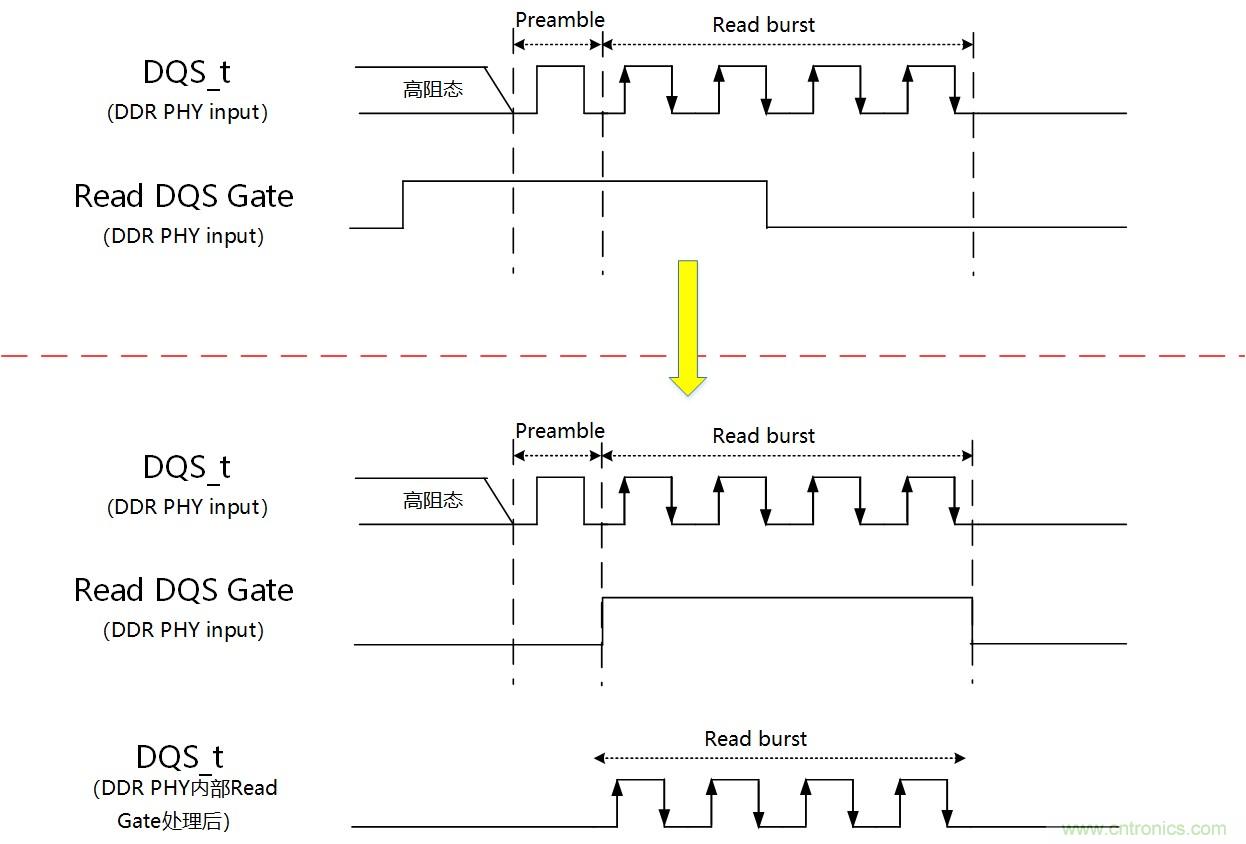

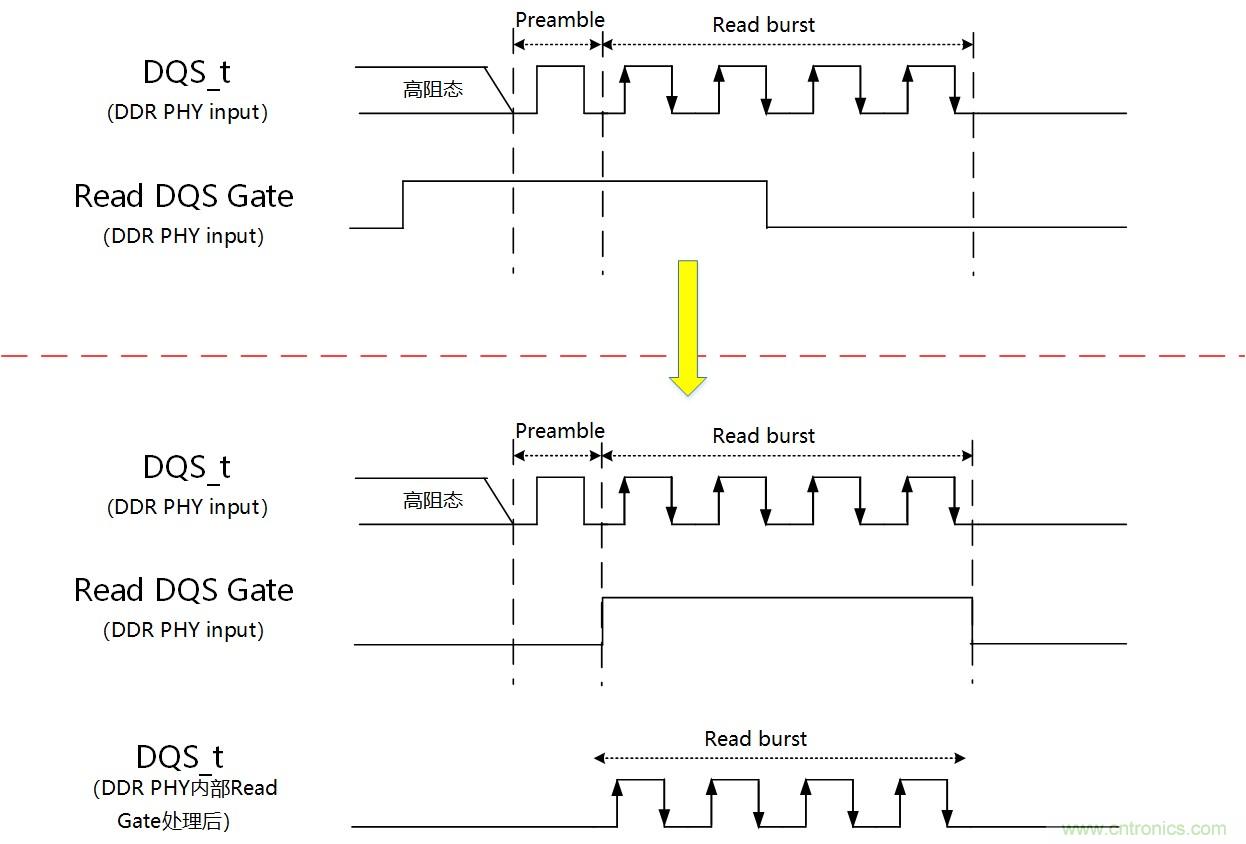

過(guò)濾訓(xùn)練時(shí)DQS的高阻態(tài)

讀操作時(shí)�����,DQS信號(hào)在前導(dǎo)(preamble)前是高阻態(tài),同時(shí)DQS信號(hào)的前導(dǎo)部分也不能達(dá)到最穩(wěn)定的狀態(tài)�,所以需要訓(xùn)練出讀DQS的gate信號(hào)來(lái)過(guò)濾掉前面的高阻態(tài)和前導(dǎo),恰好得到整個(gè)讀突發(fā)(Read Burst)操作的有效DQS�,這就是讀DQS gate訓(xùn)練。

芯耀輝采用特定的方法���,在訓(xùn)練的時(shí)候,排除不穩(wěn)定DQS的干擾���,用讀DQS的gate信號(hào)得到讀突發(fā)數(shù)據(jù)對(duì)應(yīng)的第一個(gè)DQS的上升沿位置����,從而得到gate的位置�。

圖6:讀DQS gate訓(xùn)練

延遲DQS提高讀DQ訓(xùn)練的準(zhǔn)確性

一般在DDR PHY中沒(méi)有這個(gè)訓(xùn)練,因?yàn)樵撚?xùn)練不是固態(tài)技術(shù)協(xié)會(huì)標(biāo)準(zhǔn)要求的�,可是在實(shí)際應(yīng)用中,這個(gè)訓(xùn)練卻有著比較重要的意義�。

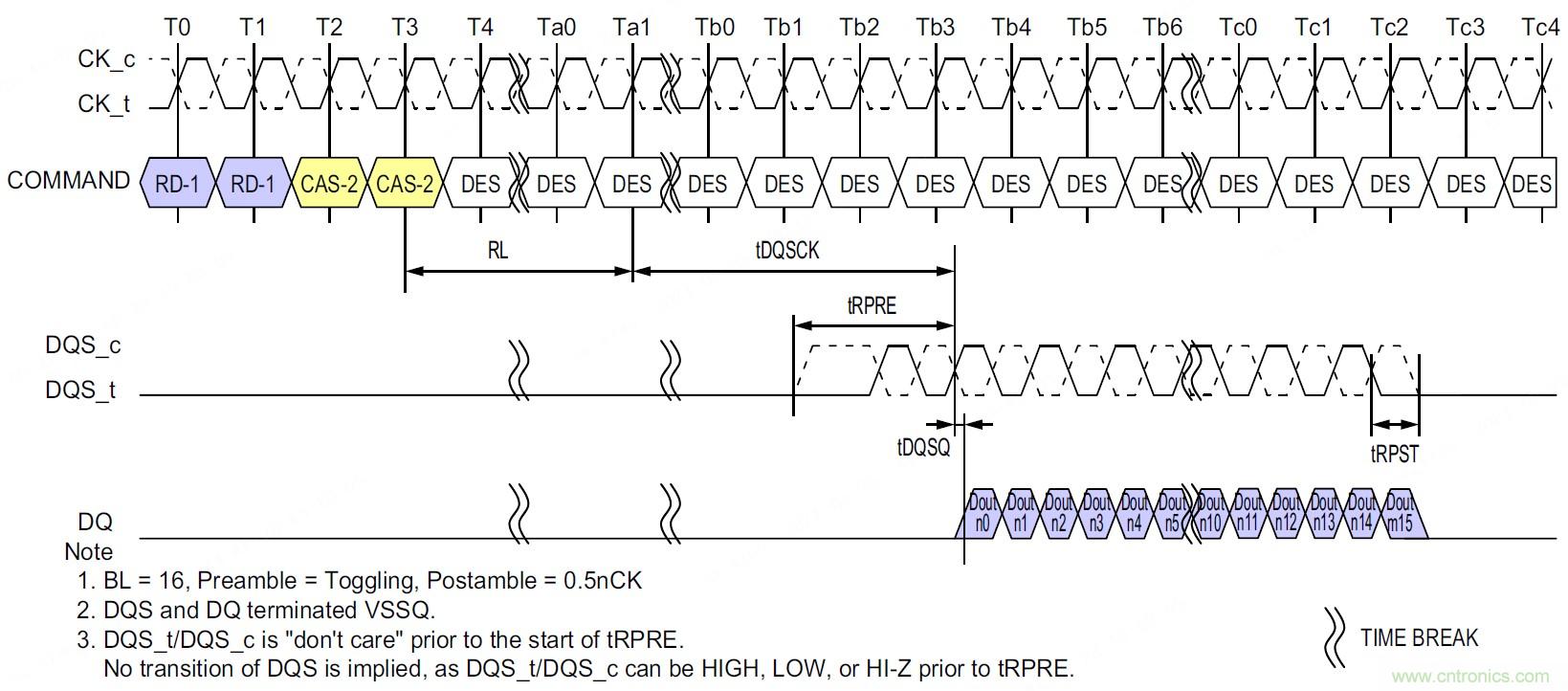

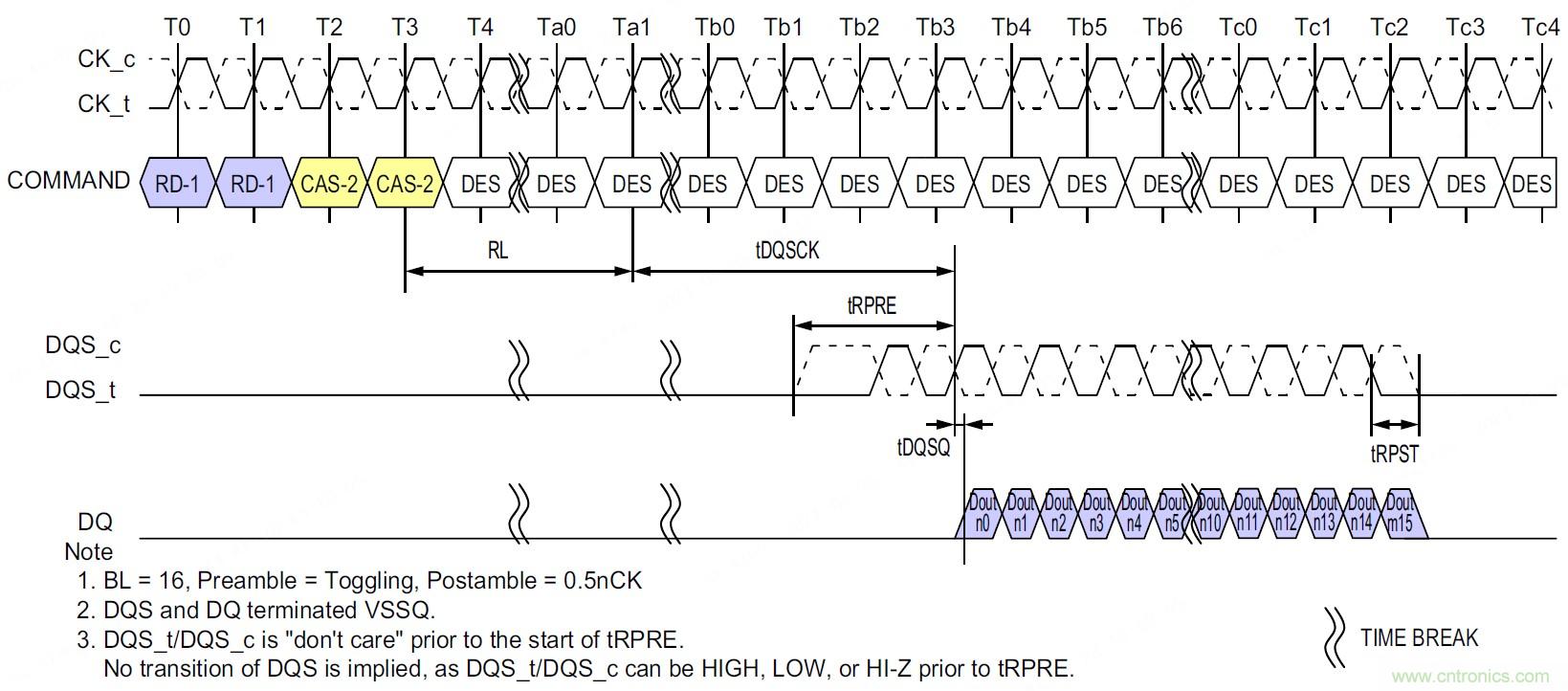

圖7:LPDDR4突發(fā)讀(來(lái)源固態(tài)技術(shù)協(xié)會(huì)標(biāo)準(zhǔn)JESD209-4B)

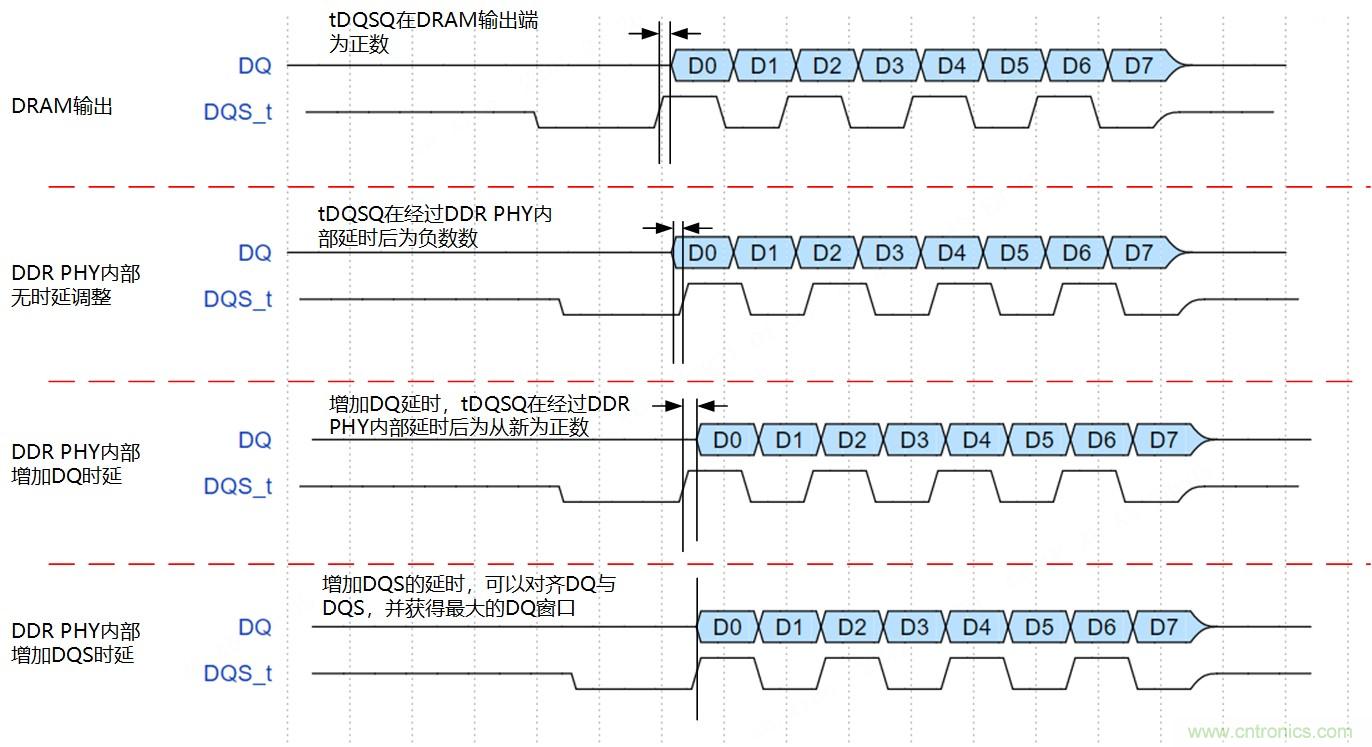

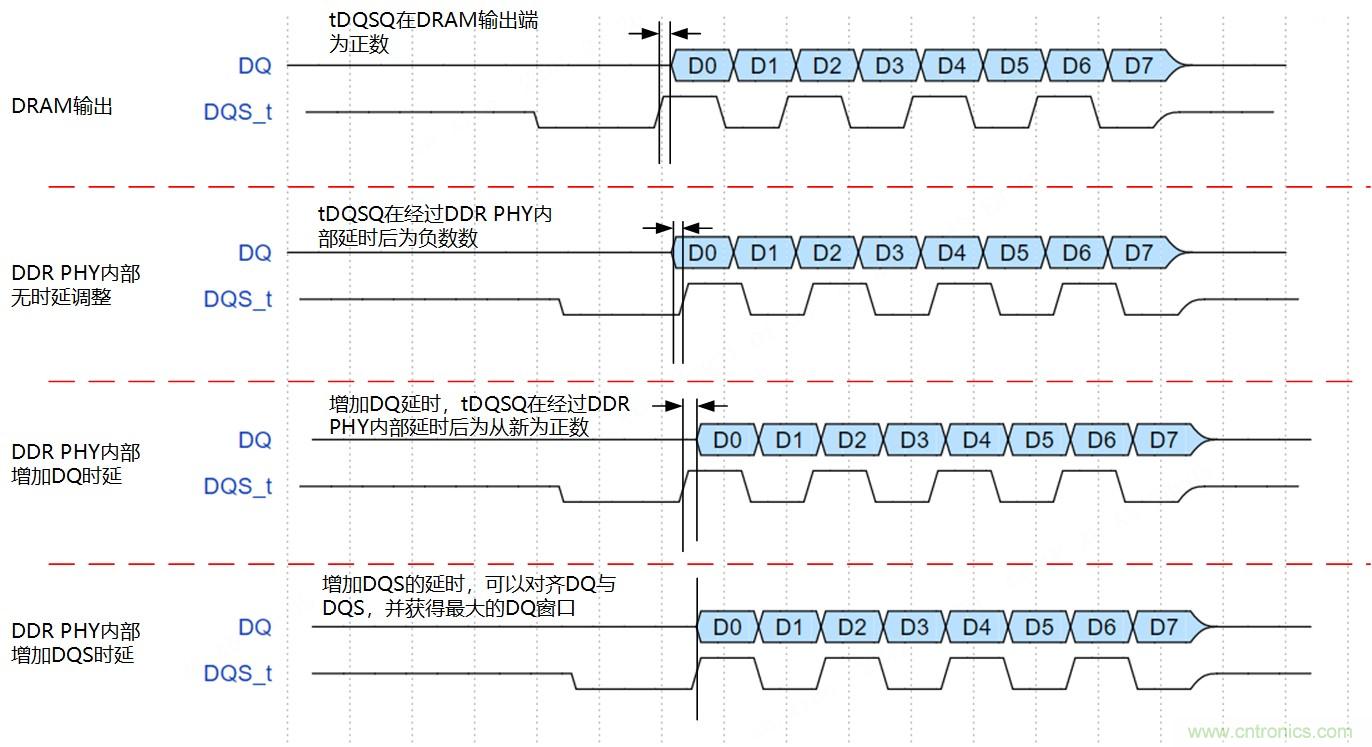

讀DQS和讀DQ之間的偏差為tDQSQ,這個(gè)值的范圍是0~0.18UI(在高頻下約為0~42ps)����。讀訓(xùn)練的時(shí)候���,采用延遲DQS的方法,找到DQ的左右窗口�,最后把DQS放在DQ窗口的中心點(diǎn)。由于DDR PHY內(nèi)部的DQS-DQ延遲偏差�、封裝的pad延遲偏差、以及PCB走線偏差�����,雖然DRAM端輸出的tDQSQ為正數(shù)(DQ的延遲比DQS大)�,但在DDR PHY內(nèi)部看到的tDQSQ卻可能為負(fù)數(shù)(DDR PHY內(nèi)部DQS的延遲比DQ大),如圖8上半部分所示�。

在這種情況下,即使DQS的延遲為0��,DQS也落在DQ的窗口內(nèi)�,PHY內(nèi)部會(huì)通過(guò)從0延遲開(kāi)始增加DQS的延遲來(lái)搜索DQ的左右窗口,這樣必然導(dǎo)致最終搜索到的DQ的窗口比實(shí)際的窗口要小���,讀訓(xùn)練后的DQS的采樣點(diǎn)不在DQ的正中間�,而在偏右的位置�,最終讀余量(margin)變小。

芯耀輝通過(guò)特定的方法�����,能讓每個(gè)DQ的窗口都在DQS右邊,這樣做讀訓(xùn)練的時(shí)候����,可以搜索到DQ的完整窗口,提高了讀訓(xùn)練的準(zhǔn)確性�,提升DDR的讀性能。

圖8:Read DQ skew training

用固件的訓(xùn)練方法獲取讀數(shù)據(jù)眼圖(Read data eye)的優(yōu)化值

讀數(shù)據(jù)眼圖訓(xùn)練通過(guò)延遲讀DQS的方法�����,把讀DQS放在DQ窗口的中間��。目前最大的問(wèn)題是固態(tài)技術(shù)協(xié)會(huì)標(biāo)準(zhǔn)對(duì)讀數(shù)據(jù)眼圖的讀序列定義的比較簡(jiǎn)單�,比如對(duì)于DDR4��,定義的序列是01010101的固定序列�。因?yàn)楦咚傩盘?hào)的符號(hào)間干擾以及信號(hào)反射,在不同的讀序列的情況下DQ窗口是有差異的����,所以采用簡(jiǎn)單固定的序列并不能很好地覆蓋實(shí)際的使用場(chǎng)景,導(dǎo)致訓(xùn)練結(jié)果在實(shí)際工作時(shí)并不是一個(gè)優(yōu)化值���。

芯耀輝采用固件的訓(xùn)練方法��,可以設(shè)置不同的范式(pattern)���,如PRBS范式����、特殊設(shè)計(jì)的掃頻范式等�����。顯然此類范式能更好地反映數(shù)據(jù)通道的特性����,因?yàn)樗烁哳l、中頻���、低頻信息��,以及長(zhǎng)0和長(zhǎng)1帶來(lái)的碼間串?dāng)_等問(wèn)題���,可以獲得較優(yōu)的訓(xùn)練結(jié)果,從而得到一個(gè)能覆蓋實(shí)際工作場(chǎng)景的可靠值��。

二維訓(xùn)練模式下優(yōu)化的參考電壓(Vref)電壓和地址線(CA)延遲

LPDDR3中引入了地址線訓(xùn)練,DRAM把采樣到的地址信號(hào)通過(guò)數(shù)據(jù)通路反饋給DDR PHY����,DDR PHY可以通過(guò)這個(gè)反饋去調(diào)節(jié)地址線的延遲。在LPDDR4中��,還加入了地址線參考電壓的訓(xùn)練�,所以不僅需要調(diào)節(jié)地址線的延遲,還需要找到一個(gè)最優(yōu)的參考電壓值����。傳統(tǒng)使用硬件訓(xùn)練的方式在面對(duì)這種兩個(gè)維度的訓(xùn)練時(shí)就會(huì)顯得捉襟見(jiàn)肘,同時(shí)硬件算法也沒(méi)法做得太復(fù)雜�。

芯耀輝采用固件的二維訓(xùn)練模式,可以繪制出完整的以地址線延遲為橫坐標(biāo)和以參考電壓為縱坐標(biāo)的二維圖像���,從而得到較優(yōu)的參考電壓和對(duì)應(yīng)的地址線延遲。

二維訓(xùn)練模式下優(yōu)化的DQ參考電壓和DQ延遲

DDR4的固態(tài)技術(shù)協(xié)會(huì)標(biāo)準(zhǔn)中引入了DQ參考電壓����,可是對(duì)于如何訓(xùn)練并沒(méi)有給出說(shuō)明和支持,所以大多數(shù)DDR PHY并不支持DDR4的DQ參考電壓訓(xùn)練����,只能配置一個(gè)固定參考電壓值�。

LPDDR4的固態(tài)技術(shù)協(xié)會(huì)標(biāo)準(zhǔn)增加了寫(xiě)DQS-DQ訓(xùn)練(調(diào)整寫(xiě)DQ相對(duì)于寫(xiě)DQS的相位)和DQ參考電壓訓(xùn)練協(xié)議上的支持�。

芯耀輝采用固件的方式,不僅支持了DDR4的DQ參考電壓訓(xùn)練����,同時(shí)對(duì)于LPDDR4的寫(xiě)DQS-DQ和DQ參考電壓訓(xùn)練,也采用了固件的二維訓(xùn)練模式�����,繪制出完整的以DQ延遲為橫坐標(biāo)和以DQ參考電壓為縱坐標(biāo)的二維圖像�,在整個(gè)二維圖像中找到較優(yōu)的DQ參考電壓和對(duì)應(yīng)的DQ延遲。

總結(jié)

隨著工藝節(jié)點(diǎn)的提升和DDR顆粒技術(shù)的演進(jìn)��,DDR的工作頻率越來(lái)越高��,DDR顆粒的訓(xùn)練要求也越來(lái)越高����。同時(shí)對(duì)于DDR PHY來(lái)說(shuō),內(nèi)部的模擬電路(FFE��,DFE等)隨著頻率的提升也需要做各種高精度的訓(xùn)練���。芯耀輝采用軟硬結(jié)合的智能訓(xùn)練方法不僅可以支持DDR顆粒的各種必要的復(fù)雜訓(xùn)練��,也同時(shí)可以支持DDR PHY內(nèi)部模擬電路的各種訓(xùn)練����。通過(guò)不斷優(yōu)化訓(xùn)練算法,持續(xù)挑戰(zhàn)每一代DDR產(chǎn)品的速率極限�����。

百尺竿頭�,更進(jìn)一步,芯耀輝人必將以提供高性能的接口類IP��,高品質(zhì)的設(shè)計(jì)服務(wù)為己任�,奮發(fā)圖強(qiáng),攜手廣大芯片設(shè)計(jì)公司推出更優(yōu)秀的產(chǎn)品���,助力中國(guó)芯片產(chǎn)業(yè)的發(fā)展��。