【導讀】相對于低頻電路需要做復雜的電路匹配,高頻電路結(jié)構(gòu)相對簡單,可簡單的結(jié)構(gòu)往往意味著需要考慮更多的問題。拿最常見的AC耦合電容來講,要么在芯片之間加兩顆直連,要么在芯片與連接器之間加兩顆。看似簡單,但一切都因為高速而不同。高速使這顆電容變得不“理想”,這顆電容沒有設(shè)計好,可能會導致整個項目的失敗。因此,對高速電路而言,這顆AC耦合電容沒有優(yōu)化好將是“致命”的。

下面筆者依據(jù)之前的項目經(jīng)驗,盤點分析一下我在這顆電容的使用上遇到的一些問題。

最開始要先明白AC耦合電容的作用。一般來講,我們用AC耦合電容來提供直流偏壓,就是濾出信號的直流分量,使信號關(guān)于0軸對稱。既然是這個作用,那么這顆電容是不是可以放在通道的任何位置呢?這就是筆者最初做高頻電路時,在這顆電容使用上遇到的第一個問題——AC耦合電容到底該放在哪。

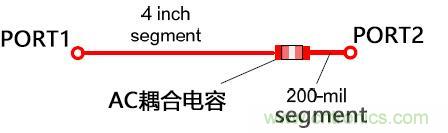

這里拿一個項目中常遇到典型的通路來分析。

圖1:AC耦合電容典型通路

在低速電路設(shè)計中,這顆電容可以等效成理想電容。而在高頻電路中,由于寄生電感的存在以及板材造成的阻抗不連續(xù)性,實際上這顆電容不能看作是理想電容。這里信號頻率2.5G,通道長度4000mil,AC耦合電容的位置分別在距離發(fā)送端和接收端200mil的位置。我們看一下仿真出的眼圖的變化。

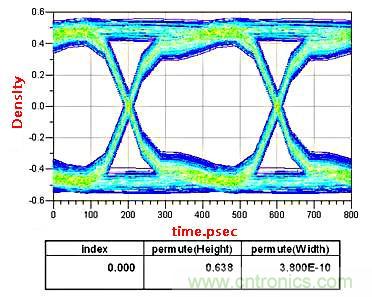

圖2:AC耦合電容靠近發(fā)送端的眼圖

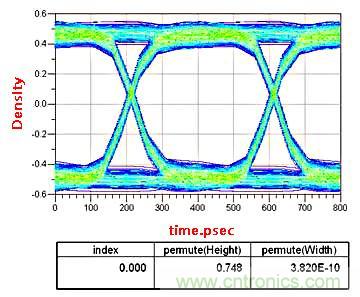

圖3:AC耦合電容靠近接收端的眼圖

顯然,這顆AC耦合電容靠近接收端的時候信號的完整性要好于放在發(fā)送端。我的理解是這樣的,非理想電容器阻抗不連續(xù),信號經(jīng)過通道衰減后反射的能量會小于直接反射的能量,所以絕大多數(shù)串行鏈路要求這顆AC耦合電容放在接收端。但也有例外,筆者之前做板對板連接時遇到過這個問題,查PCIE規(guī)范發(fā)現(xiàn)如果是兩個板通常放置在發(fā)送端上,此時還利用到了AC耦合電容的另外一個作用——過壓保護。比如說SATA,所以通常要求靠近連接器放置。

解決了放置的問題,另一個困擾大家的就是容值的選取了。這樣說,我們的整個串行鏈路等效出的電阻R是固定的,那么AC耦合電容C的選取將會關(guān)系到時間常數(shù)(RC),RC越大,過的直流分量越大,直流壓降越低。既然這樣,AC耦合電容可以無限增大嗎?顯然是不行的。

圖4:AC耦合電容增大后測量到的眼圖

同樣的位置,與圖3相比可以看出增大耦合電容后,眼高變低。原因是“高速”使電容變的不理想。感應(yīng)電感會產(chǎn)生串聯(lián)諧振,容值越大,諧振頻率越低,AC耦合電容在低頻情況下呈感性,因此高頻分量衰減增大,眼高變小,上升沿變緩,相應(yīng)的JITTER也會增大。通常建議AC耦合電容在0.01uf~0.2uf之間,項目中0.1uf比較常見。推薦使用0402的封裝。

最后,解決了以上兩個問題,再從PCB設(shè)計上分析一下這顆電容的優(yōu)化設(shè)計。實際在項目中,與AC耦合電容的位置、容值大小這些可見因素相比,更加難以捉摸的是板材本身(包括焊盤的精度、銅箔的均勻度等)以及焊盤處的寄生電容對信號完整性的影響。我們知道,高頻信號必須沿著有均勻特征阻抗的路徑傳播,如果遇到阻抗失配或者不連續(xù)的情況時,部分信號會被反射回發(fā)射端,造成信號的衰減,影響信號的完整性。項目中,這種情況通常會出現(xiàn)在焊盤或者是板載連接器處。筆者最初涉及的高速電路設(shè)計時,經(jīng)常遇到這個問題。

解決這個問題要從兩個方面入手。首先在板材的選取上,我們在應(yīng)用中通常選用高性能的ROGERS板材,羅杰斯的板材在銅箔厚度的控制上非常精確,均勻的銅箔覆蓋大大降低了阻抗的不連續(xù)性;然后在消除焊盤處的寄生電容上,業(yè)內(nèi)常見的辦法是在焊盤處做隔層處理(挖空位于焊盤正下方的參考平面區(qū)域,在內(nèi)層創(chuàng)建銅填充),通過增大焊盤與其參考平面(或者是返回路徑)之間的距離,減小電容的不連續(xù)性。在筆者的項目中多采用介質(zhì)均勻、銅箔寬度控制精確的ROGERS板材也有效提高了焊盤的加工精度。

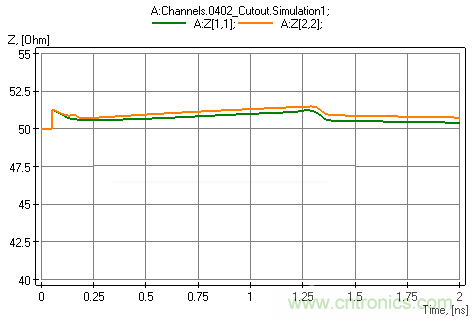

通過仿真對比一下ROGERS板材做精確隔層處理前后的信號完整性。

圖5:做隔層處理前的TDR

圖6:做隔層處理后的TDR

圖5圖6對比,發(fā)現(xiàn)未處理之前阻抗的跳躍很明顯,隔層處理后的阻抗改善很多,幾乎沒有任何階躍與不連續(xù)。

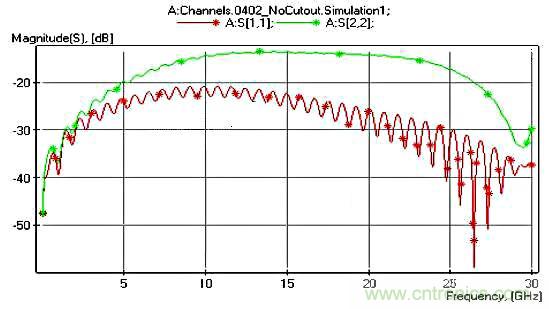

圖7:做隔層處理前的回波損耗

圖8:做隔層處理后的回波損耗

圖7圖8對比,在用ROGERS板材做隔層處理之后,相比未做隔層處理回波損耗下降到-30dB之內(nèi),大大降低了回波損耗,保證了信號傳輸?shù)耐暾?/div>

綜上,想要搞定高頻電路中這顆“致命”的AC耦合電容,不僅要做足電路設(shè)計上的功課,同時,選擇性能更好的高頻PCB板材料會讓你事半功倍。