【導(dǎo)讀】通過使用Achronix Speedster7t FPGA中的機器學(xué)習(xí)加速器MLP72,開發(fā)人員可以輕松選擇浮點/定點格式和多種位寬,或快速應(yīng)用塊浮點,并通過內(nèi)部級聯(lián)可以達到理想性能。

通過使用Achronix Speedster7t FPGA中的機器學(xué)習(xí)加速器MLP72,開發(fā)人員可以輕松選擇浮點/定點格式和多種位寬,或快速應(yīng)用塊浮點,并通過內(nèi)部級聯(lián)可以達到理想性能。

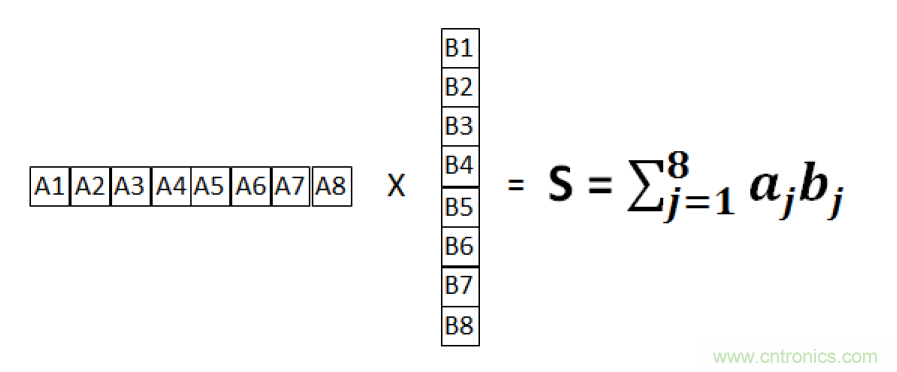

神經(jīng)網(wǎng)絡(luò)架構(gòu)中的核心之一就是卷積層,卷積的最基本操作就是點積。向量乘法的結(jié)果是向量的每個元素的總和相乘在一起,通常稱之為點積。此向量乘法如下所示:

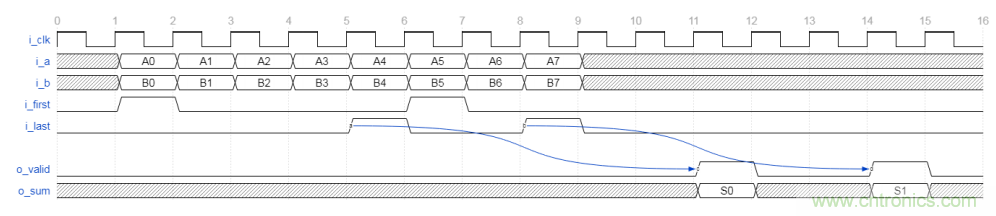

圖1點積操作

該總和S由每個矢量元素的總和相乘而成,因此

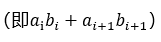

本文講述的是使用FP16格式的點積運算實例,展示了MLP72支持的數(shù)字類型和乘數(shù)的范圍。

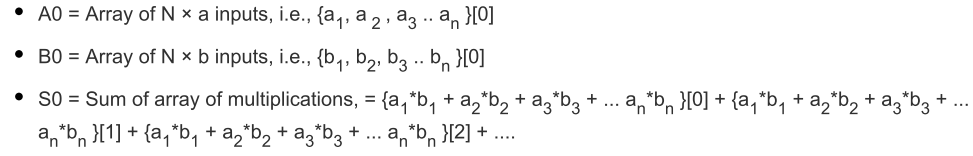

此設(shè)計實現(xiàn)了同時處理8對FP16輸入的點積。該設(shè)計包含四個MLP72,使用MLP內(nèi)部的級聯(lián)路徑連接。每個MLP72將兩個并行乘法的結(jié)果相加 ,每個乘法都是i_a輸入乘以i_b輸入(均為FP16格式)的結(jié)果。來自每個MLP72的總和沿著MLP72的列級聯(lián)到上面的下一個MLP72塊。在最后一個MLP72中,在每個周期上,計算八個并行FP16乘法的總和。

,每個乘法都是i_a輸入乘以i_b輸入(均為FP16格式)的結(jié)果。來自每個MLP72的總和沿著MLP72的列級聯(lián)到上面的下一個MLP72塊。在最后一個MLP72中,在每個周期上,計算八個并行FP16乘法的總和。

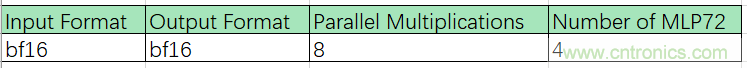

最終結(jié)果是多個輸入周期內(nèi)的累加總和,其中累加由i_first和i_last輸入控制。i_first輸入信號指示累加和歸零的第一組輸入。i_last信號指示要累加和加到累加的最后一組輸入。最終的i_last值可在之后的六個周期使用,并使用i_last o_valid進行限定。兩次運算之間可以無空拍。

配置說明

表1 FP16點積配置表

端口說明

表2 FP16點積端口說明表

時序圖

圖2 FP16點積時序圖

其中,

那么,以上運算功能如何對應(yīng)到MLP內(nèi)部呢?其后的細(xì)節(jié)已分為MLP72中的多個功能階段進行說明。

進位鏈

首先請看下圖,MLP之間的進位鏈結(jié)構(gòu),這是MLP內(nèi)部的專用走線,可以保證級聯(lián)的高效執(zhí)行。

圖3 MLP進位鏈

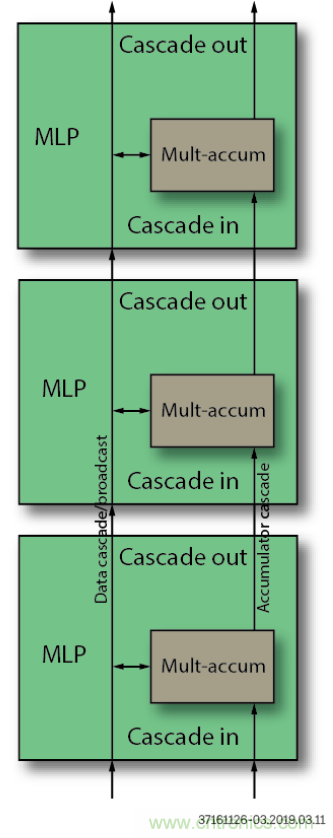

乘法階段

下圖是MLP中浮點乘法功能階段,其中寄存器代表一級可選延遲。

圖4 MLP乘法功能階段框圖

MLP72浮點乘法級包括兩個24位全浮點乘法器和一個24位全浮點加法器。兩個乘法器執(zhí)行A×B和C×D的并行計算。加法器將兩個結(jié)果相加得到A×B + C×D。

乘法階段有兩個輸出。下半部分輸出可以在A×B或(A×B + C×D)之間選擇。上半部分輸出始終為C×D。

乘法器和加法器使用的數(shù)字格式由字節(jié)選擇參數(shù)以及和參數(shù)設(shè)置的格式確定。

浮點輸出具有與整數(shù)輸出級相同的路徑和結(jié)構(gòu)。MLP72可以配置為在特定階段選擇整數(shù)或等效浮點輸入。輸出支持兩個24位全浮點加法器,可以對其進行加法或累加配置。進一步可以加載加法器(開始累加),可以將其設(shè)置為減法,并支持可選的舍入模式。

最終輸出階段支持將浮點輸出格式化為MLP72支持的三種浮點格式中的任何一種。此功能使MLP72可以外部支持大小一致的浮點輸入和輸出(例如fp16或bfloat16),而在內(nèi)部以fp24執(zhí)行所有計算。

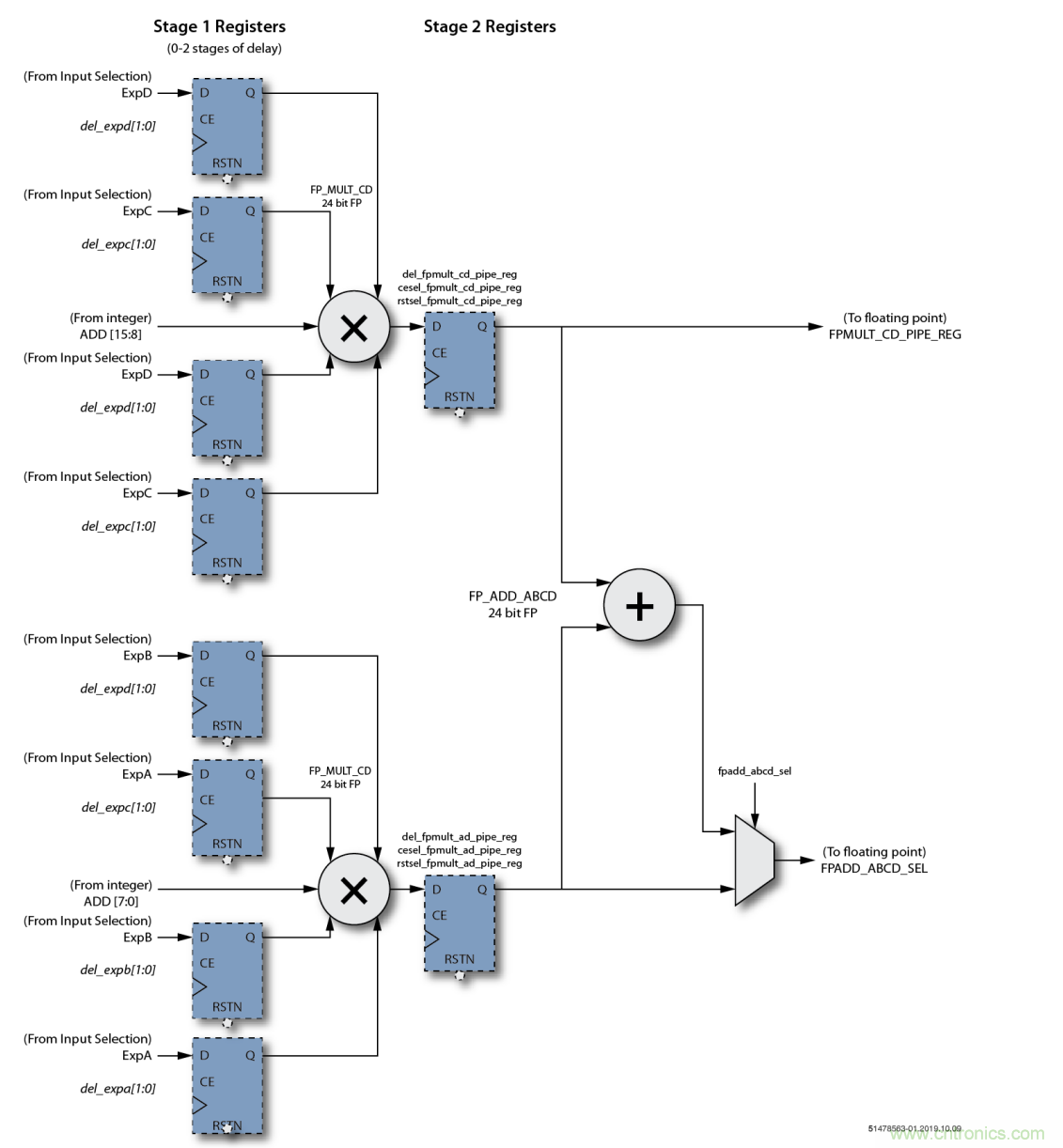

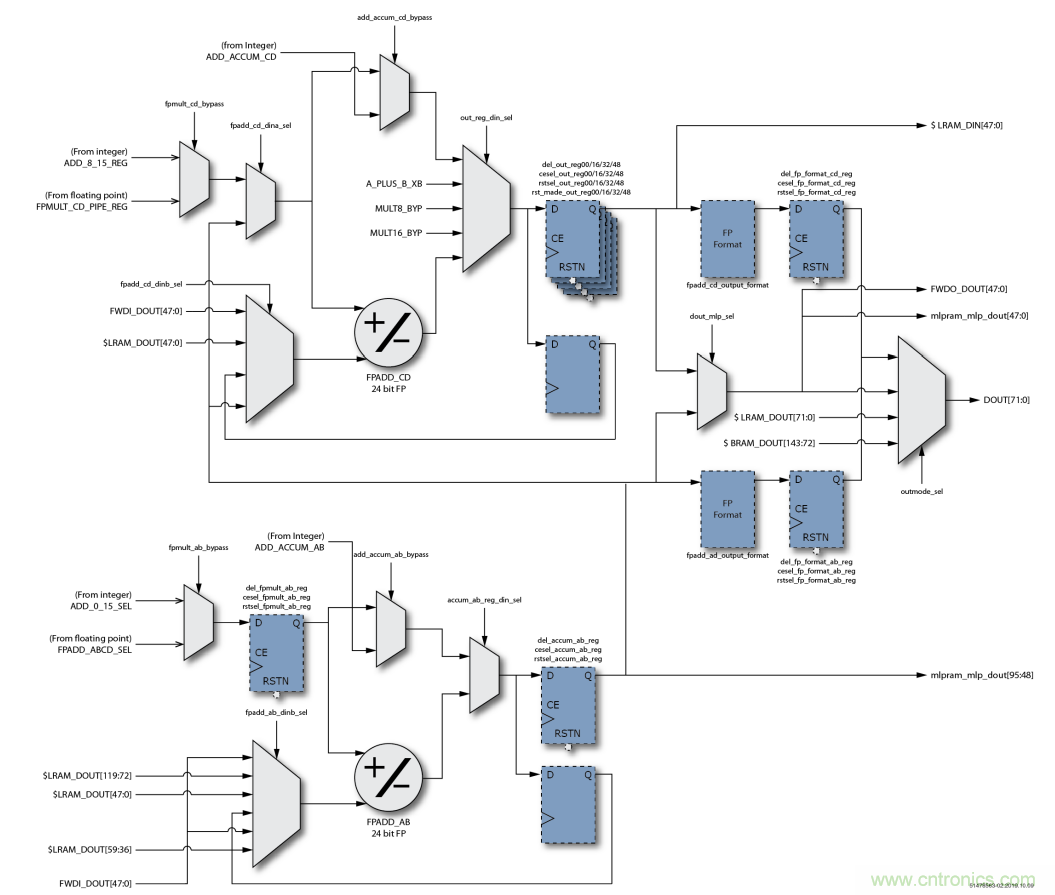

圖5 MLP浮點輸出階段框圖

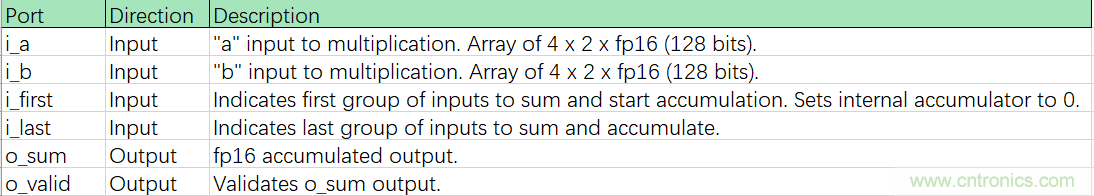

需要強調(diào)的是本設(shè)計輸入和輸出都是FP16格式,中間計算過程,即進位鏈上的fwdo_out和fwdi_dout 都是FP24格式。具體邏輯框圖如下所示:

圖6 FP16點積邏輯框圖

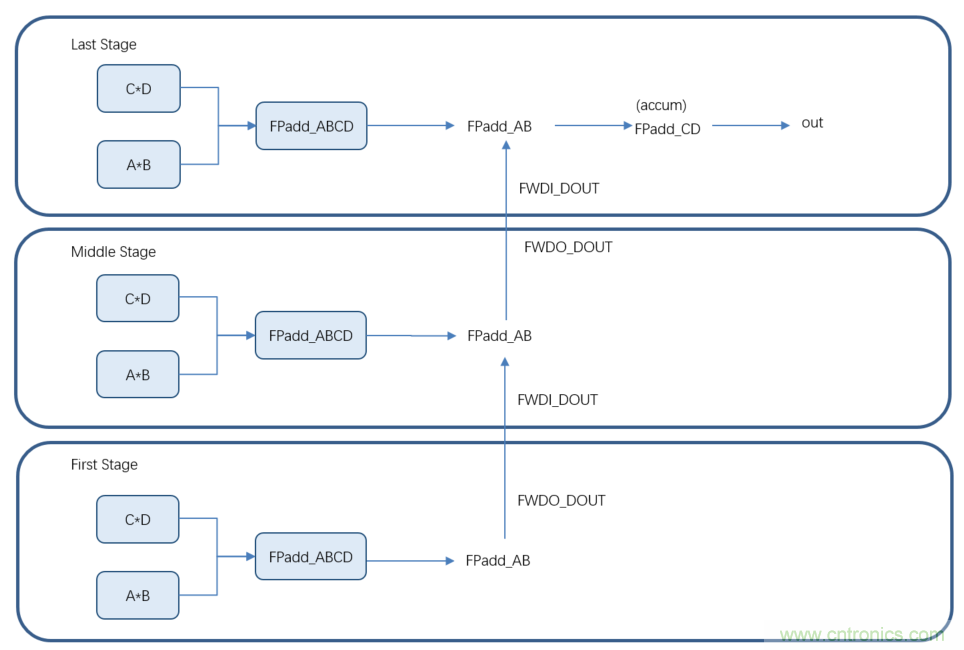

MLP內(nèi)部數(shù)據(jù)流示意圖:

圖7 FP16點積在MLP內(nèi)部數(shù)據(jù)流圖

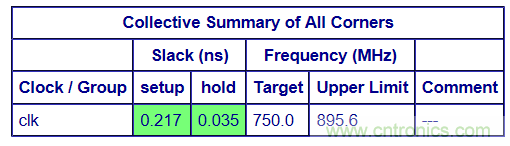

最終ACE的時序結(jié)果如下:

(來源:Achronix,作者:楊宇,Achronix資深現(xiàn)場應(yīng)用工程師)

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請電話或者郵箱聯(lián)系小編進行侵刪。