【導(dǎo)讀】Vishay Siliconix設(shè)計和生產(chǎn)面向工業(yè)、可再生能源、計算、消費及照明市場的高壓MOSFET(HVM)。我們擁有電壓范圍為50V至1000V的廣泛器件,其中采用我們最新超結(jié)技術(shù)的器件的電壓范圍為500 V至650 V 。本設(shè)計指南的目的是幫助設(shè)計工程師在其功率因數(shù)校正(PFC)設(shè)計中實現(xiàn)盡可能高的MOSFET效率。

功率因數(shù)校正設(shè)計

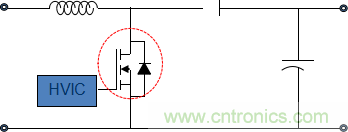

如圖1所示的PFC校正電路塊是一個重要子系統(tǒng),在許多情況下是輸出功率不低于65 W的電源的必備子系統(tǒng)(依據(jù)EN61000-3-2)。該電路用于使輸入線路電流與AC電壓波形相配,在大多數(shù)情況下使輸出電壓上升至常見的400 VDC。

圖1:功率因數(shù)校正原理圖

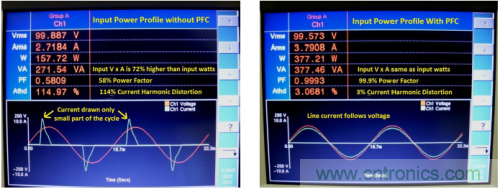

“功率因數(shù)”為實際功率(P = 瓦特)與表觀功率(VA = 伏安)的比率。這方面的目標(biāo)是實現(xiàn)盡可能接近于1的單位功率因數(shù)。對于完全相同的輸出功率,低功率因數(shù)負(fù)載比高功率因數(shù)負(fù)載會消耗更多無功電流。較低功率因數(shù)設(shè)計的較大電流會增加系統(tǒng)的能量損失,造成電力公司在輸電過程中浪費大量電能。圖1a和1b顯示了PFC對線路電流及其諧波的影響。

圖1a. 沒有PFC電路的線路電壓和電流 1b. 具有PFC電路的波形

在沒有PFC的圖1a中,電流只在周期的短時間期間來自AC電源。這導(dǎo)致較差的功率因數(shù)和高達(dá)115 %的過多諧波。雖然系統(tǒng)只使用了158 W可用功率,但輸電系統(tǒng)為提供它卻消耗了272伏安。圖2a顯示了在相同線路上實施PFC的好處。這時功率因數(shù)為99.9 %,諧波降至3 %。電流在整個周期中都來自AC線路,沒有浪費過多VA成分。

可以注意到,功率因數(shù)校正和諧波電流下降并非同義詞。例如,在高度電感性負(fù)載中,電流可能以完美正弦波形滯后于電壓。這會導(dǎo)致較差的功率因數(shù)和高無功功率,沒有任何諧波。而諧波電流豐富的失真波形通常具有所有不合需要的特性。PFC電路不只校正功率因數(shù),還降低諧波電流。

目前,有多種不同標(biāo)準(zhǔn)規(guī)定了電子設(shè)備所用電力的質(zhì)量。EN61000-3-2要求輸入功率大于75 W的所有系統(tǒng)都要降低諧波電流。80 Plus電流認(rèn)證要求功率因數(shù)為0.9或更高。

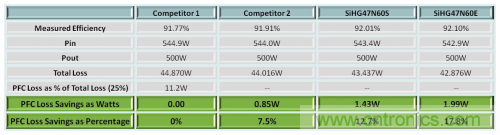

在PFC電路中,MOSFET的損耗占總損耗的約15 %至20 %。在使用校正器件后,PFC效率可實現(xiàn)總共0.33 %增加(表1)。在500 W輸出功率下,計算結(jié)果是MOSFET功率損耗可減小2 W。

表1:基于總PFC功率損耗的MOSFET損耗計算

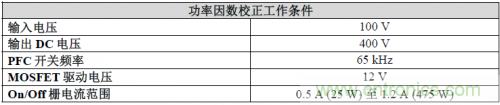

Vishay Siliconix針對規(guī)定的工作條件和5 W至1000 W輸出功率級編制了最重要的兩種600 V和650 V器件的列表,以幫助設(shè)計工程師在PFC設(shè)計中選擇最合適的MOSFET。表2列出了規(guī)定的工作條件,表4列出了每種功率級的最重要兩種E系列超結(jié)技術(shù)器件。雖然主要標(biāo)準(zhǔn)是效率,但表中提供了不止一種器件選擇,以滿足成本、封裝或更高電壓降額等其他要求。

PFC設(shè)計開發(fā)使用的MOSFET器件列表

表4中的器件是使用針對新應(yīng)用的品質(zhì)因數(shù)(FOM)而選擇的,該品質(zhì)因數(shù)側(cè)重于最大限度減小器件的總損耗。雖然包括針對導(dǎo)電損耗的導(dǎo)通電阻(RDS(on))和針對開關(guān)損耗的柵電荷(Qg),但FOM并非簡單的二者之積。為說明開關(guān)損耗,使用了器件的Qgs和Qgd的一部分及其輸出容值(Coss)。選擇最合適的器件時使用了以下工作條件(參見表2)。

表2:功率因數(shù)校正設(shè)計條件

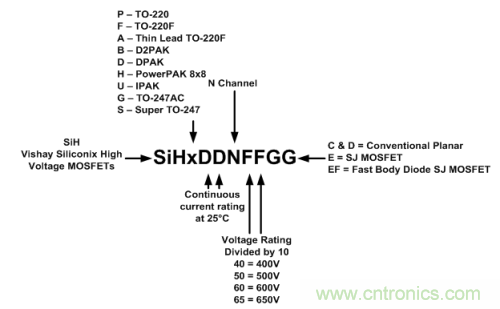

推薦器件的列表在“封裝”位置包括一個“x”。在相同電氣特征下,每種器件有許多可選封裝。實際使用的封裝取決于功率級和允許的MOSFET占位面積。圖2定義了不同零件號的封裝、額定電流、電壓和器件技術(shù)

定義:Vishay高壓MOSFET零件號:SiHxDDNFFGG

圖2:零件號定義

對于提供的許多封裝選項,表3列出了不同封裝的建議最大額定功率。

基于封裝類型的推薦功率等級

表3:基于封裝類型的最大功率級

注:

* 如果使用散熱性能增強的多層PCB,則該封裝可在更高功率級下使用。

** 如果使用交錯式(interleaved)PFC設(shè)計,則輸出功率最大可達(dá)750 W(使用兩個TO-220)。在非交錯式設(shè)計中并聯(lián)兩個TO-220或TO-220F允許最大750 W。

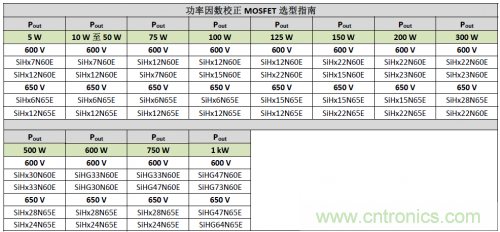

結(jié)合設(shè)計條件、器件零件號含義和每種封裝類型的最大建議值,表4顯示了針對不同功率級的相應(yīng)器件。

該列表顯示了許多不同器件。設(shè)計工程師可按照電壓、效率或價格來挑選最適合自己應(yīng)用的器件。

功率因數(shù)校正MOSFET選型指南

表4:基于PFC輸出功率級的器件選型工具

帶有“x”的器件可使用多種封裝;帶有“G”的器件必須使用TO-247封裝。