【導讀】在上一篇文章“多種DC-DC技術合力應對電源設計的挑戰(zhàn)(一)”中,我們介紹了開關式轉換器拓撲的改進和如何改善輕負載條件。在本文中,我們將介紹封裝技術和新材料對電源效率的提升。

新的封裝技術幫助設計人員提高功率密度

另一種增加功率密度的方式是減小所需的PCB面積。其中一種方法便是將組件結合到DC/DC模塊中。Texas Instruments提供的MicroSiP和MicroSiL電源模塊,在電源轉換器中集成了無源元件和集成電路(IC),將IC嵌入到FR4層壓基板上,并在基材上安裝電感器,以此構成單個設備。

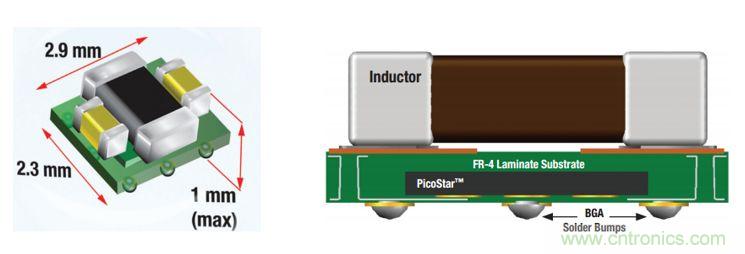

完全集成的MicroSiP電源模塊將IC和無源元件集成到一個最高集成級別的設備中。最小的模塊使用BGA封裝形式,其占位面積不足7mm²。

圖1:MicroSiP封裝將集成電路嵌入到基板中,并將無源元件堆在頂部,以組成微型DC-DC轉換器(資料來源:Texas Instruments)

MicroSiL設備集成了電感器和調節(jié)器IC,并使用了外部電容器。該模塊的引腳分配和輪廓類似于QFN封裝。例如,TPS82085電源模塊是同步降壓轉換器,可以從3mm×2.8mm的8引腳封裝傳輸3A的電流。

集成可以大幅減少元器件的占位面積,但是需要權衡利弊得失。例如,MicroSiP封裝在控制器的上面放了電感器,并將組件安裝在PCB上。與分立設計相比,這些特性都會增加MicroSiP模塊的高度。

要盡量縮減占位面積,還需要減小電感器的尺寸。線圈電感與其面積和圈數(shù)成正比,所以為了不改變電感,減少面積,就需要增加使用的電線,但同時也會導致增加線圈的DC電阻。

超越硅的設計:SiC和GaN器件

為了追求更高的性能,設計人員開始探索硅之外的其他材料。用SiC和GaN制造的電子元器件開始在一些電力應用中取代硅器件,前二者都屬于寬帶隙(WBG)半導體。

我們先來回顧一下什么是固體帶隙,固體的帶隙用于衡量價帶頂部和導帶底部之間的能量差(eV),是確定材料導電性的主要因素。

硅的帶隙為1.1eV,相比之下,WBG半導體的帶隙分別為3.3V(SiC)和3.4V(GaN),因此,需要更多的能量將電子從價帶傳輸?shù)綄А_@對于功率半導體而言比較有優(yōu)勢:與硅相比,WBG器件具有更低的導通電阻、更高的擊穿電壓、出色的反向恢復特性,并且可以在更高的開關頻率下工作。

更高的開關頻率允許使用更小的電容器、電感器和變壓器,其尺寸、重量和成本都大為節(jié)省。同時,DC-DC轉換效率可以最高提升10%。

Texas Instruments最近發(fā)布了一款LMG5200,將WBG半導體與高級封裝結合在了一起。LMG5200是半橋功率級,在一個QFN封裝中集成了兩個80V的GaN功率場效應管(FET)和一個高頻GaN驅動器。LMG5200將與現(xiàn)有產品(如TPS53632)配對使用,服務于各種應用,包括用于計算、工業(yè)和電信應用的同步降壓轉換器和48V POL轉換器。

總結

提升電力轉換解決方案的效率和功率密度需要采用多學科綜合的方法,借鑒控制器設計、封裝和半導體研究方面的專業(yè)知識。只有集各領域之所長,設計人員才能滿足眾多應用的需求,這些應用從電池驅動的低功耗可穿戴設備和便攜式設備,到高功率的電信交換機和數(shù)據(jù)中心等,范圍十分廣泛。

本文轉載自貿澤電子。

本文轉載自貿澤電子。

推薦閱讀: