【導(dǎo)讀】當(dāng)現(xiàn)成的運(yùn)算放大器(op amp)不能提供特定應(yīng)用所需的信號擺幅范圍時(shí),工程師面臨兩種選擇:使用高壓運(yùn)算放大器或設(shè)計(jì)分立解決方案,不過這兩種選擇的成本可能都很高。

對許多應(yīng)用來說,第三種選擇——自舉——可能是比較廉價(jià)的替代方案。除了動(dòng)態(tài)性能要求極為苛刻的應(yīng)用,自舉電源電路的設(shè)計(jì)是相當(dāng)簡單的。

自舉簡介

常規(guī)運(yùn)算放大器要求其輸入電壓在其電源軌范圍內(nèi)。如果輸入信號可能超過電源軌,可以通過電阻衰減過大輸入,使這些輸入降至電源范圍以內(nèi)的電平。這樣處理并不理想,因?yàn)樗鼤?huì)對輸入阻抗、噪聲和漂移產(chǎn)生不利影響。同樣的電源軌也會(huì)限制放大器輸出,閉環(huán)增益的大小存在一個(gè)限值,以避免將輸出驅(qū)動(dòng)到飽和狀態(tài)。

因此,如果要求處理輸入和/或輸出上的大信號偏離,則需要寬電源軌和能在這些電源軌上工作的放大器。ADI 的 24V 至 220V 精密運(yùn)算放大器 ADHV4702-1 是適合這種情況的出色選擇,不過自舉低壓運(yùn)算放大器也能滿足應(yīng)用要求。是否使用自舉主要取決于動(dòng)態(tài)要求和功耗限制。

自舉會(huì)創(chuàng)建一個(gè)自適應(yīng)雙電源,其正負(fù)電壓不是以地為基準(zhǔn),而是以輸出信號的瞬時(shí)值為基準(zhǔn),有時(shí)稱之為飛軌(flying rail) 配置。在這種配置中,電源隨著運(yùn)算放大器的輸出電壓(VOUT) 上下移動(dòng)。因此,VOUT始終處于中間電源電壓,并且電源電壓能夠相對于地移動(dòng)。使用自舉可以非常容易地實(shí)現(xiàn)這種自適應(yīng)雙電源。

實(shí)際上,自舉必須符合一些準(zhǔn)則,有些準(zhǔn)則微不足道,但沒有一個(gè)準(zhǔn)則是特別麻煩的。如下是最基本的準(zhǔn)則:

● 輸出負(fù)載不得過大。

● 響應(yīng)速度不得低于運(yùn)算放大器的壓擺率。

● 必須能處理所需的電壓水平和相關(guān)的功耗。

工作原理

飛軌概念是指正負(fù)電源軌連續(xù)調(diào)整,使其電壓始終關(guān)于輸出電壓對稱。這樣,輸出始終位于電源范圍內(nèi)。

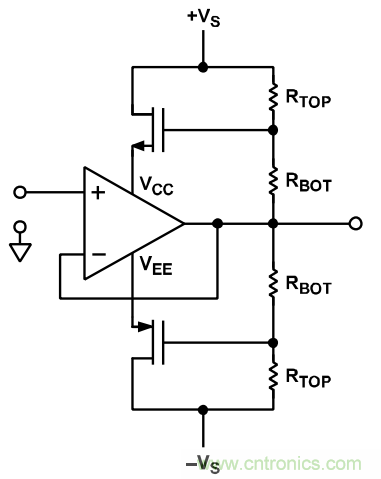

電路架構(gòu)包括一對互補(bǔ)分立晶體管和一個(gè)阻性偏置網(wǎng)絡(luò)。 NPN 發(fā)射極(或 N 溝道 MOSFET 的源極引腳)提供 VCC, PNP 發(fā)射極(或 P 溝道 MOSFET 的源極引腳)用作 VEE。晶 體管被偏置,使得所需的電源電壓出現(xiàn)在放大器的+VS和–VS 引腳上,這些電壓通過電阻分壓器從高壓電源獲得。圖 1 顯 示了簡化高壓跟隨器原理圖。

圖 1. 簡化高壓跟隨器原理圖

理論上,自舉可以為任何運(yùn)算放大器提供任意高的信號順從電壓。而在實(shí)際上,電源調(diào)整比例越大,動(dòng)態(tài)性能越差,因?yàn)檫\(yùn)算放大器的壓擺率限制了電源對動(dòng)態(tài)信號的響應(yīng)速度。放大器在最大額定電源電壓或接近該電壓下工作時(shí),電源引腳為跟上動(dòng)態(tài)信號而需要橫越的范圍最小。當(dāng)運(yùn)算放大器在接近其最高額定電源電壓下工作時(shí),其他誤差源(如噪聲增益)也會(huì)降低。

不需要電源移動(dòng)很遠(yuǎn)(或非常快)的低頻和直流應(yīng)用,是自舉的最佳候選應(yīng)用。因此,高壓放大器能提供比動(dòng)態(tài)特性相當(dāng)?shù)牡蛪悍糯笃鞲玫膭?dòng)態(tài)性能,尤其是當(dāng)二者均偏置為各自的最大工作電源電壓并且自舉到相同信號范圍時(shí)。自舉也會(huì)影響直流性能,因此在直流精度和高電壓兩方面均經(jīng)過優(yōu)化的運(yùn)算放大器可提供自舉配置能實(shí)現(xiàn)的最佳直流和交流性能組合。

舉例:采用ADHV4702-1 的范圍擴(kuò)展器的設(shè)計(jì)考慮

ADHV4702-1 是一款精密 220 V運(yùn)算放大器。有了該器件,就不需要自舉傳統(tǒng)低壓運(yùn)算放大器,220 V以下信號范圍的高壓設(shè)計(jì)得以簡化。如果應(yīng)用需要更高電壓,那么可以應(yīng)用自舉技術(shù),輕松地將電路工作范圍增加兩倍以上。下面說明一個(gè)基于ADHV4702-1 的 500 V放大器設(shè)計(jì)示例。

電壓范圍

如上所述,擴(kuò)展器電路的范圍在理論上是無限的,但存在如下一些實(shí)際限制:

● 電源電壓和電流額定值

● 電阻和場效應(yīng)晶體管(FET)功耗

● FET 擊穿電壓

直流偏置電平

首先,考慮提供給放大器的電源電壓。任何在器件額定電源電壓范圍內(nèi)的電壓都有效。然而,功耗是基于所選擇的工作電壓在放大器和 FET 之間分配。對于給定的原始電源電壓,運(yùn)算放大器電源電壓越低,F(xiàn)ET 中的漏源電壓(VDS)越高,功耗也相應(yīng)地進(jìn)行分配。應(yīng)選擇適當(dāng)?shù)倪\(yùn)算放大器電源電壓,從而以最有利于散熱的方式在器件之間分配功耗。其次,使用下式計(jì)算將原始電源電壓(VRAW)降低到放大器期望電源電壓(VAMP)所需的分壓比:

其中,RTOP為頂部電阻,RBOT為底部電阻。

對于下例,考慮運(yùn)算放大器標(biāo)稱電源電壓為±100 V。對于需要±250 V 擺幅范圍的應(yīng)用,通過下式計(jì)算分壓比:

然后,使用便于獲得的標(biāo)準(zhǔn)值電阻設(shè)計(jì)電阻分壓器,盡可能接近地實(shí)現(xiàn)此分壓比。請注意,由于涉及高電壓,電阻功耗可能比預(yù)期要高。

靜態(tài)功耗

對于所選電阻值,應(yīng)選擇能夠應(yīng)對相應(yīng)靜態(tài)功耗的電阻尺寸。相反,如果電阻的物理尺寸受限,應(yīng)選擇適當(dāng)?shù)碾娮柚祦韺⑸嵯拗圃陬~定范圍內(nèi)。

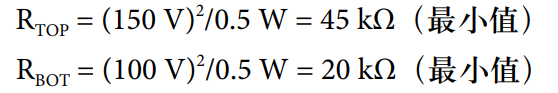

在該示例中,RTOP達(dá)到 150 V,RBOT達(dá)到 100 V。使用額定功率為 1 /2瓦的 2512 電阻,設(shè)計(jì)必須將每個(gè)電阻器的功耗(V2/R) 限制在 0.5 W 以下。計(jì)算每個(gè)電阻的最小值,如下所示:

將較高值電阻(45kΩ)作為功耗的限制因素,RBOT 值產(chǎn)生一個(gè) 2.5:1 分壓器,同時(shí)觀測靜態(tài)功耗限值為

其功耗為(100 V)2/30 kΩ = 0.33 W。

瞬時(shí)功耗

考慮到電阻的瞬時(shí)電壓取決于放大器的輸出電壓以及電源電壓,本例中任何時(shí)刻每個(gè)分壓器上的電壓可能高達(dá)350 V(VCC = 250 V 且 VOUT = –100 V)。正弦輸出波形在 VCC和 VEE分壓器中產(chǎn)生 相同的平均功耗,但任何非零平均輸出都會(huì)導(dǎo)致一個(gè)分壓器 的功耗高于另一個(gè)分壓器的功耗。對于滿量程直流輸出(或方波),瞬時(shí)功耗為最大功耗。

在此示例中,為將瞬時(shí)功耗保持在 0.5 W 以下,每個(gè)分壓器中兩個(gè)電阻之和(RSUM)不得小于以下值:

因此,電阻比為 1.5:1(對于 2.5:1 分壓器)時(shí),各個(gè)電阻的最小值如下:

● RTOP = 147 kΩ

● RBOT = 98 kΩ

FET 選擇

承受最壞情況偏置條件所需的擊穿電壓主要決定 FET的選擇;當(dāng)輸出飽和,使得一個(gè) FET 處于最大 VDS,另一個(gè) FET 處于最小 VDS 時(shí),便可明白這一點(diǎn)。在前面的示例中,最 高絕對 VDS 約為 300 V,即總原始電源電壓(500 V)減去放大器的總電源電壓(200 V)。因此,F(xiàn)ET 必須承受至少 300 V 電壓而不被擊穿。

功耗必須針對最壞情況 VDS 和工作電流來計(jì)算,并且必須選擇指定在此功率水平下工作的 FET。

接下來考慮 FET 的柵極電容,因?yàn)樗鼤?huì)與偏置電阻一起形成一個(gè)低通濾波器。擊穿電壓較高的 FET 往往具有較高的柵極電容,而且偏置電阻往往為 100 kΩ,因此不需要多少柵極電容就能顯著降低電路的速度。從制造商的數(shù)據(jù)手冊中獲得柵極電容值,計(jì)算 RTOP和 RBOT并聯(lián)組合所形成的極點(diǎn)頻率。

偏置網(wǎng)絡(luò)的頻率響應(yīng)必須始終快于輸入和輸出信號,否則放大器的輸出可能超出其自身的電源范圍。暫時(shí)偏離到放大器電源軌之外會(huì)有損壞輸入的風(fēng)險(xiǎn),而暫時(shí)飽和或壓擺受限會(huì)有造成輸出失真的風(fēng)險(xiǎn)。任何一種狀況都可能導(dǎo)致負(fù)反饋暫時(shí)丟失和不可預(yù)測的瞬態(tài)行為,甚至可能因?yàn)槟承┻\(yùn)算放大器架構(gòu)中的相位反轉(zhuǎn)而閂鎖。

性能

直流線性度

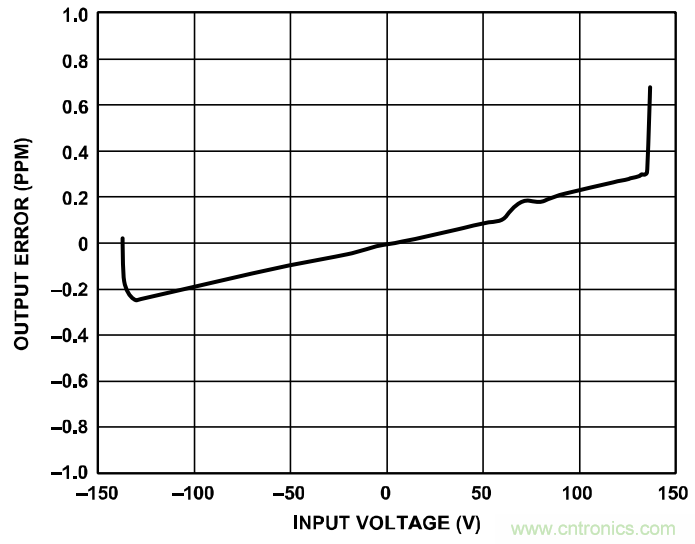

圖 2 顯示了增益誤差與輸入電壓的關(guān)系(直流線性度),增益為 20,電源為±140 V。

圖2. 增益誤差與輸入電壓的關(guān)系

壓擺率

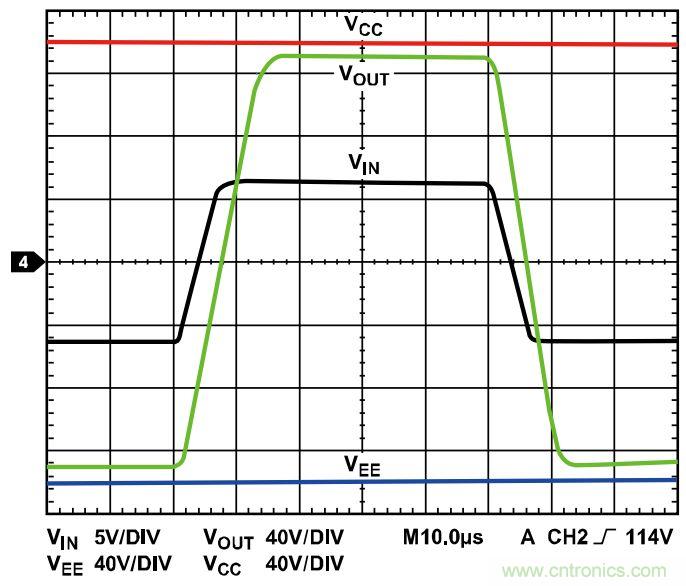

圖 3 顯示了壓擺率曲線,增益為 20,電源為±140 V,測量值為 20.22 V/μs。

圖 3. 壓擺率

實(shí)現(xiàn)更高速度的權(quán)衡

功耗

如前所述,工作電壓較高時(shí),F(xiàn)ET 的擊穿電壓(和相關(guān)的柵極電容)以及電阻值也必須較高。較高的電阻和電容值都會(huì)造成帶寬降低,唯一可用的調(diào)整因素是電阻值。降低電阻值會(huì)提高帶寬,但代價(jià)是功耗增加。

空間

低阻值、高功率的電阻尺寸較大,需占用較多電路板空間。以電容的形式在RBOT上增加一些引線補(bǔ)償可以改善電路的頻率響應(yīng)。此電容與 RBOT和 RTOP電阻形成一個(gè)零點(diǎn),抵消 FET 柵極電容所形成的極點(diǎn)。極點(diǎn)和零點(diǎn)相消,因此可以選擇更高阻值的電阻,從而降低直流功耗。

結(jié)論

在需要較高電壓但使用典型高壓運(yùn)算放大器不經(jīng)濟(jì)的應(yīng)用中,常常會(huì)讓常規(guī)運(yùn)算放大器自舉。自舉有其優(yōu)點(diǎn)和缺點(diǎn)。還有一個(gè)選擇,ADHV4702-1 提供一種高達(dá) 220 V的精密高性能解決方案,無需自舉。但是,當(dāng)信號范圍要求超過 220 V時(shí), 該器件可以自舉以處理超過標(biāo)稱信號范圍兩倍以上的電壓,同時(shí)提供比自舉低壓放大器更高的性能。

推薦閱讀: