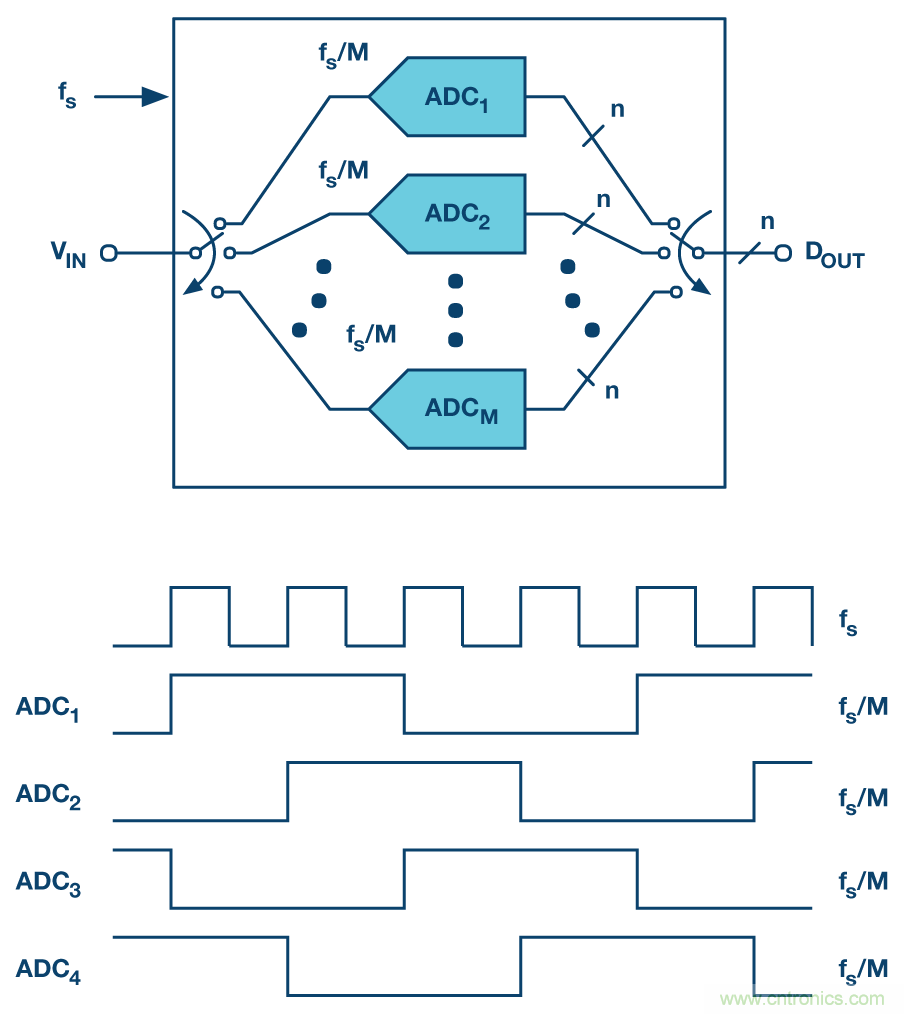

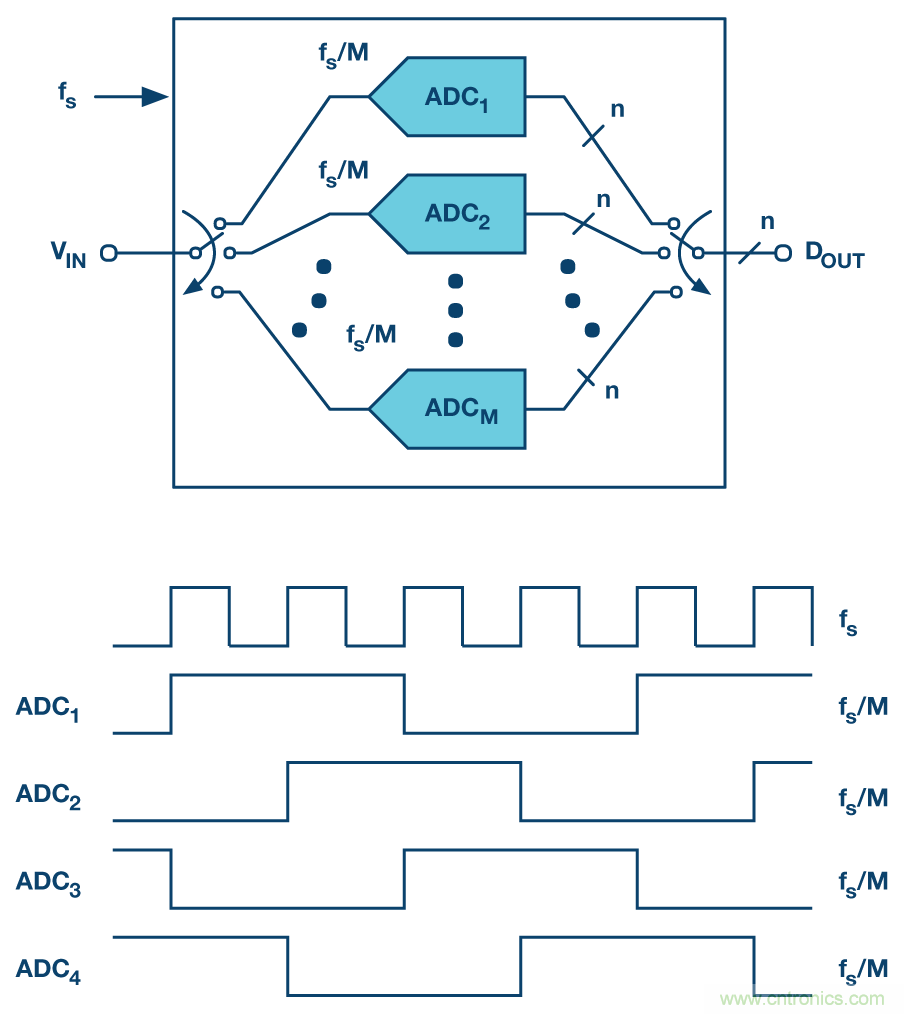

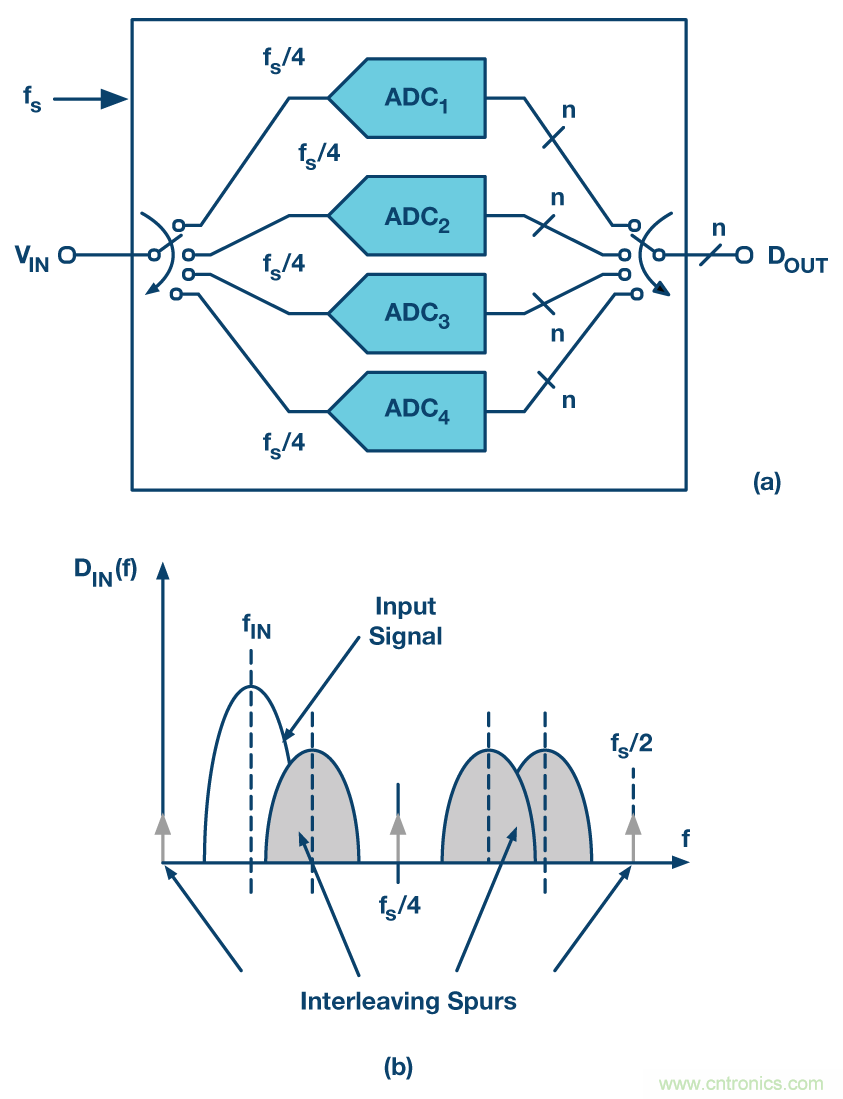

【導(dǎo)讀】時(shí)間交錯(cuò)技術(shù)可使用多個(gè)相同的模數(shù)轉(zhuǎn)換器[1] (ADC),并以比每一個(gè)單獨(dú)數(shù)據(jù)轉(zhuǎn)換器工作采樣速率更高的速率來(lái)處理常規(guī)采樣數(shù)據(jù)序列�����。簡(jiǎn)單說(shuō)來(lái)���,時(shí)間交錯(cuò)(IL)由時(shí)間多路復(fù)用M個(gè)相同的ADC并聯(lián)陣列組成����,如圖1所示��。這樣可以得到更高的凈采樣速率fs(采樣周期Ts = 1/fs),哪怕陣列中的每一個(gè)ADC實(shí)際上以較低的速率進(jìn)行采樣(和轉(zhuǎn)換)�����,即fs/M。因此�����,舉例而言��,通過(guò)交錯(cuò)四個(gè)10位/100 MSPS ADC,理論上可以實(shí)現(xiàn)10位/400 MSPS ADC����。

為了更好地理解IL原理,圖1中一個(gè)模擬輸入VIN (t)以M個(gè)ADC進(jìn)行采樣���,其結(jié)果為組合數(shù)字輸出數(shù)據(jù)序列DOUT�。ADC1最先采樣VIN (t0)并開(kāi)始將其轉(zhuǎn)換為n位數(shù)字信號(hào)�����。Ts秒后,ADC2將采樣VIN (t0+Ts)并開(kāi)始將其轉(zhuǎn)換為n位數(shù)字信號(hào)����。接著,Ts秒后����,ADC3將采樣VIN (t0 +2Ts)��,以此類推����。ADCM完成VIN (t0 +(M-1)×Ts)采樣后,開(kāi)始下一個(gè)采樣周期���,并從ADC1采樣VIN (t0 +M×Ts)開(kāi)始�����,依次進(jìn)行下去��。

由于ADC順序輸出n位數(shù)據(jù)且輸出順序與剛才描述的采樣操作順序一致��,這些數(shù)字n位字由同一張圖右側(cè)的解復(fù)用器所采集����。這里獲取的是重新組合的數(shù)據(jù)輸出序列DOUT (t0 + L),DOUT (t0 + L + Ts)���,DOUT (t0 + L + 2Ts)�,...。L表示每一個(gè)單獨(dú)ADC的固定轉(zhuǎn)換時(shí)間��,而該重新組合的數(shù)據(jù)序列是一個(gè)n位數(shù)據(jù)序列���,采樣速率為fs。因此�,雖然各個(gè)ADC(通常稱為"通道")為n位ADC且采樣速率為fs/M���,但整體等于采樣速率為fs的單個(gè)n位ADC�,而我們將其稱為時(shí)間交錯(cuò)ADC(與通道相區(qū)別)�。輸入本質(zhì)上是分隔開(kāi)的,并由陣列中的ADC單獨(dú)處理�,然后在輸出端連續(xù)重組,以便構(gòu)成輸入VIN的高數(shù)據(jù)速率表示DOUT�。

圖1. M次交錯(cuò)的n位ADC陣列每一個(gè)ADC的采樣速率為fs/M,得到的時(shí)間交錯(cuò)ADC采樣速率為fs����。M = 4的時(shí)鐘方案示例在該圖下半部分顯示��。

這種強(qiáng)大的技術(shù)在實(shí)際使用時(shí)存在一些難題。一個(gè)重要的問(wèn)題是來(lái)自通道的M數(shù)據(jù)流經(jīng)過(guò)數(shù)字組裝后重構(gòu)原始輸入信號(hào)VIN���。如果我們看一下頻譜DOUT;除了看到VIN的數(shù)字信號(hào)以及模數(shù)轉(zhuǎn)換引入的失真�,我們還將看到額外的和大量的雜散成分��,稱為"交錯(cuò)雜散"(或簡(jiǎn)稱為IL雜散);IL雜散既沒(méi)有多項(xiàng)式類型失真的簽名——比如較高次信號(hào)諧波(2次����,3次,等等)——也沒(méi)有量化或DNL誤差簽名。IL偽像可視為時(shí)域固定碼噪聲的一種形式,由通道中的模擬損害引起,因?yàn)樵诮诲e(cuò)過(guò)程中采用分隔轉(zhuǎn)換信號(hào)進(jìn)行調(diào)制并出現(xiàn)在最終的數(shù)字化輸出DOUT����。

讓我們分析一個(gè)簡(jiǎn)單的示例�,了解可能會(huì)發(fā)生什么情況?�?紤]頻率fIN下正弦輸入VIN的雙路交錯(cuò)ADC情況。假定ADC1具有增益G1��,ADC2具有差分增益G2�。在這種雙路IL ADC中,ADC1和ADC2將交替采樣VIN��。因此�,如果ADC1轉(zhuǎn)換偶數(shù)樣本����,而ADC2轉(zhuǎn)換奇數(shù)樣本��,則所有DOUT偶數(shù)數(shù)據(jù)的幅度都將由G1設(shè)置��,而所有DOUT奇數(shù)數(shù)據(jù)的幅度都將由G2設(shè)置����。然后,DOUT不僅包含VIN,還包括一些多項(xiàng)式失真,但它受到G1和G2的交替放大,就好像我們采用頻率為fs/2的方波對(duì)VIN進(jìn)行幅度調(diào)制���。這樣做會(huì)引入更多雜散成分�。特別地�,DOUT在fs/2 – fIN頻率處會(huì)包含"增益雜散"�����;并且不幸的是���,該雜散的頻率會(huì)跟蹤輸入fIN�����,且位于交錯(cuò)ADC的第一奈奎斯特頻段內(nèi)(即在fs/2內(nèi))�����,而在所有其它奈奎斯特頻段內(nèi)也會(huì)存在混疊。該交錯(cuò)雜散的功率/幅度取決于兩個(gè)增益G1和G2之間的凈差。換言之,它取決于增益誤差失配[2]���。而最終,它取決于輸入VIN自身的幅度����。

如果輸入并非簡(jiǎn)單正弦波�,而是真實(shí)應(yīng)用中的全頻帶限幅信號(hào),那么"增益雜散"就不只是干擾音了�����,而是頻帶限幅輸入信號(hào)自身的完整調(diào)節(jié)鏡像��,出現(xiàn)在奈奎斯特頻段內(nèi)�����。這在一定程度上抵消了交錯(cuò)帶來(lái)的帶寬增加的優(yōu)勢(shì)。

雖然上例中我們僅考慮了通道間的增益誤差失配,其它損害也會(huì)引起交錯(cuò)雜散。失調(diào)失配(通道失調(diào)之間的差)引起固定頻率的信號(hào)音("失調(diào)雜散")����,功率與失調(diào)失配成正比[3]����。當(dāng)某些通道比預(yù)定順序更早或更晚采樣某位時(shí)�����,便發(fā)生采樣時(shí)間偏斜��。它會(huì)引入"時(shí)間雜散"����,其頻率與增益雜散完全一致(并疊加同樣的幅度)[4]但功率會(huì)隨著fIN的增加以及輸入幅度的增加而不斷加強(qiáng)。各通道之間的帶寬失配會(huì)引入更多的雜散成分����,頻率取決于fIN���,并且正如時(shí)間雜散,雜散功率不僅隨著輸入幅度��,而且還會(huì)隨著fIN自身而逐步增加�。再次強(qiáng)調(diào),無(wú)論何種情況��,輸出頻譜下降的程度并不取決于通道損害的絕對(duì)值(失調(diào)�����、增益����、時(shí)序、頻段)���,而是取決于通道之間的相對(duì)失配或通道之差�。

雖然時(shí)間交錯(cuò)的基本技術(shù)存在已有幾十年�����,但I(xiàn)L可在何種程度上保持最小化則將其過(guò)去的適用性限制于低分辨率轉(zhuǎn)換器。然而�,最近在通道失配校準(zhǔn)方面以及抑制殘留IL雜散成分方面的進(jìn)步已經(jīng)可以實(shí)現(xiàn)全集成�����、極高速�、12/14/16位IL ADC。

這種情況下���,我們需要對(duì)交錯(cuò)進(jìn)行分類�。我們一般將兩個(gè)交錯(cuò)通道稱為"乒乓"工作�����。然后���,當(dāng)我們描述較少通道數(shù)的情況(比如3通道至4通道)�����,以及大量通道的情況時(shí)(比如超過(guò)4個(gè)通道��,通常達(dá)到8個(gè)或更多)�,我們還區(qū)分了"輕度交錯(cuò)"和"重度交錯(cuò)"。

乒乓(雙路)交錯(cuò)

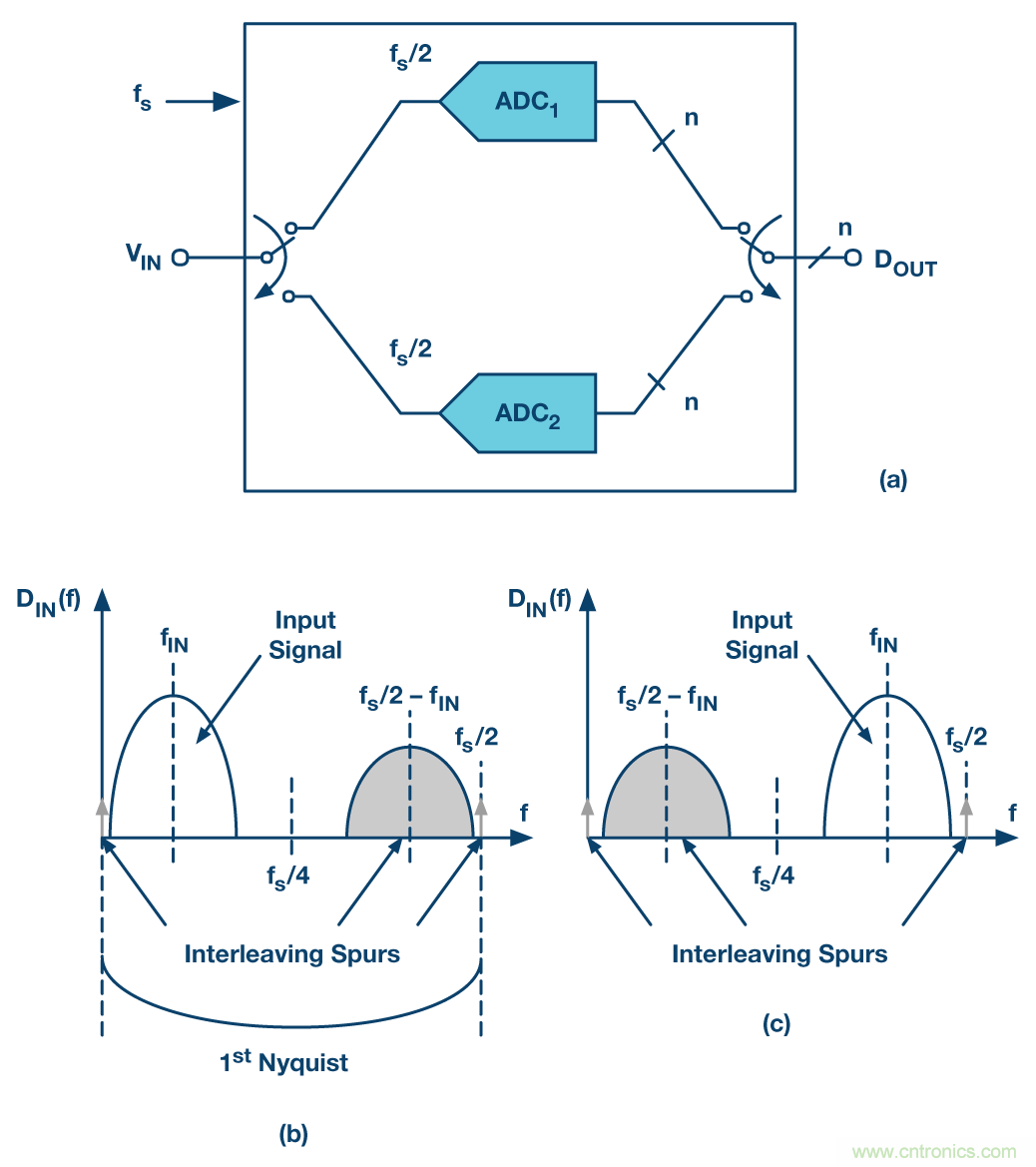

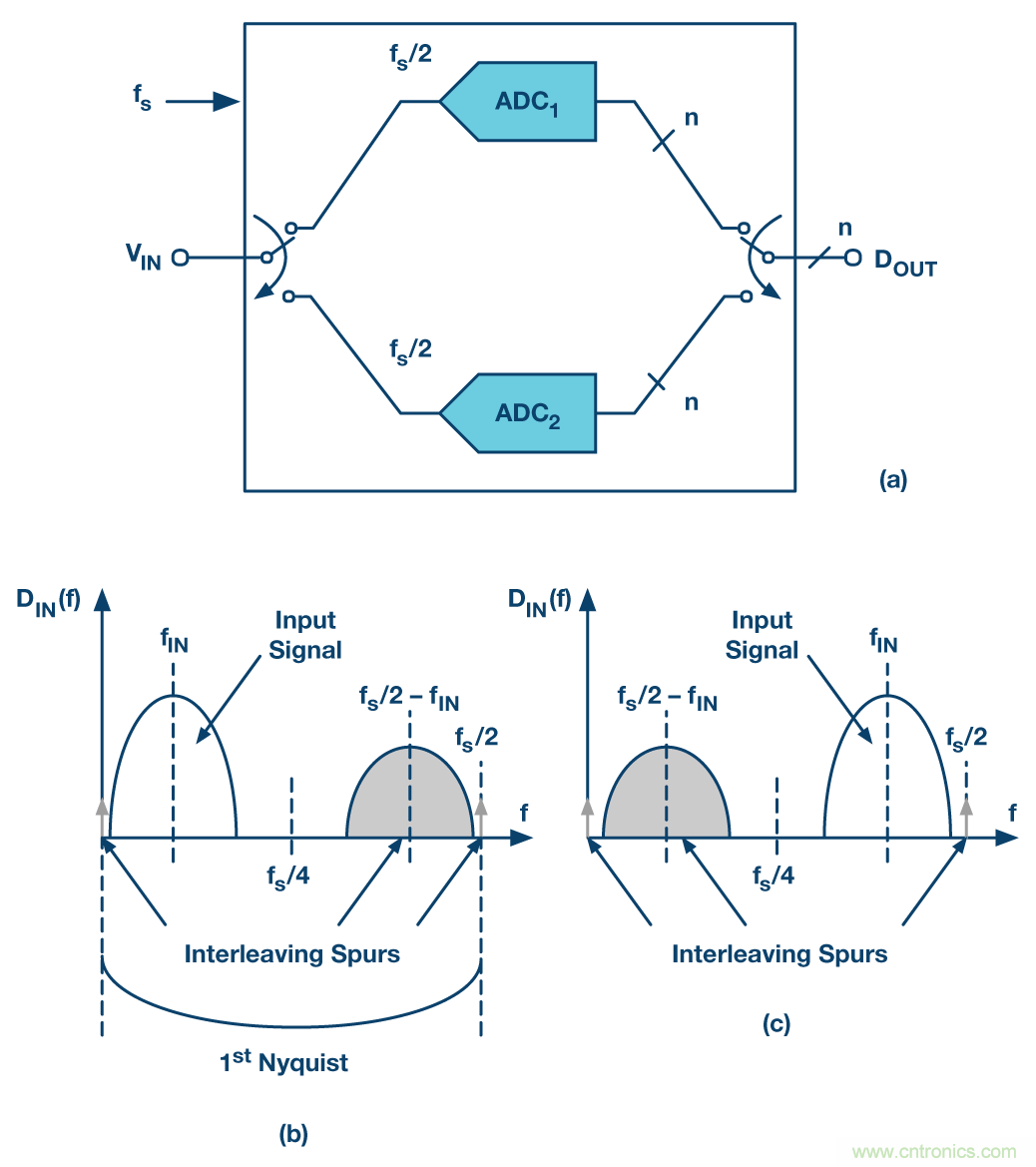

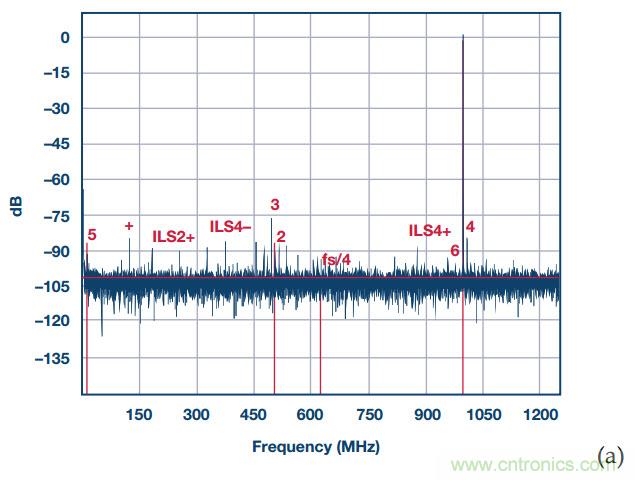

當(dāng)我們只是交錯(cuò)兩個(gè)通道以便使采樣速率翻倍時(shí)�����,我們將其稱為"乒乓"�,如圖2 (a)中的框圖所示。這是一種最簡(jiǎn)單的情況����,它有一些有趣和有用的特性。這種情況下��,在交錯(cuò)ADC的第一奈奎斯特頻段內(nèi)��,交錯(cuò)雜散位于直流��、fs/2和fs/2 – fIN處�����。因此��,如果輸入信號(hào)VIN是一個(gè)對(duì)中至fIN的窄帶信號(hào)——如圖2 (b)中的第一奈奎斯特輸出頻譜所示——交錯(cuò)雜散包含直流處的失調(diào)雜散����、fs/2處的另一個(gè)失調(diào)失配雜散以及對(duì)中至fs/2 – fIN的增益和時(shí)序雜散鏡像�,看上去就像輸入自身的一個(gè)放大復(fù)制版本�。

如果輸入信號(hào)VIN (f)完全位于0和fs/4之間——如圖2 (b)所示——那么交錯(cuò)雜散不與數(shù)字化輸入頻率重疊。此時(shí)�����,壞消息是我們只能數(shù)字化半個(gè)奈奎斯特頻段����,就好比只有一個(gè)時(shí)鐘為fs/2的單通道��,雖然我們依舊消耗至少兩倍于該單個(gè)通道的功耗����。奈奎斯特頻段上限的交錯(cuò)雜散鏡像可在數(shù)字化之后通過(guò)數(shù)字濾波手段抑制,無(wú)需進(jìn)行模擬損害校正�����。

但好消息是由于乒乓ADC時(shí)鐘為fs��,數(shù)字化輸出得益于動(dòng)態(tài)范圍內(nèi)的3 dB處理增益�����。此外,與使用時(shí)鐘為fs/2的單個(gè)ADC相比����,乒乓ADC放寬了抗混疊濾波器設(shè)計(jì)要求。

圖2. (a)乒乓方案(b)窄帶輸入信號(hào)位于fs/4以下時(shí)的輸出頻譜(c)此時(shí)輸入信號(hào)位于fs/4和奈奎斯特頻率fs/2之間��。

如果窄帶信號(hào)位于第一奈奎斯特頻段的上半部���,則所有考慮因素都適用���,如圖2 (c)所示,因?yàn)榻诲e(cuò)鏡像雜散移至奈奎斯特頻段的下半部分�。再次強(qiáng)調(diào),增益和時(shí)序雜散可在濾波數(shù)字化之后通過(guò)數(shù)字手段抑制�。

最后����,輸入信號(hào)和交錯(cuò)雜散的頻率將會(huì)重疊,并且一旦輸入信號(hào)頻率位置跨過(guò)fs/4線����,交錯(cuò)鏡像就會(huì)破壞輸入頻譜���。這種情況下,恢復(fù)所需輸入信號(hào)將是不可能的�����,而乒乓方案不可用�����。當(dāng)然�����,除非通道間匹配足夠緊密�����,使得交錯(cuò)雜散成分對(duì)于應(yīng)用來(lái)說(shuō)達(dá)到可以接受的低程度��,或者引入校準(zhǔn)來(lái)降低導(dǎo)致IL鏡像的原因��。

總之�����,頻率規(guī)劃和某些數(shù)字濾波可以恢復(fù)乒乓方案中的窄帶數(shù)字化輸入�����,哪怕存在通道失配���。雖然轉(zhuǎn)換器功耗相比使用單個(gè)時(shí)鐘為fs/2的ADC時(shí)基本翻了個(gè)倍���,但乒乓方案提供了3 dB處理增益,同時(shí)放寬了抗混疊要求����。

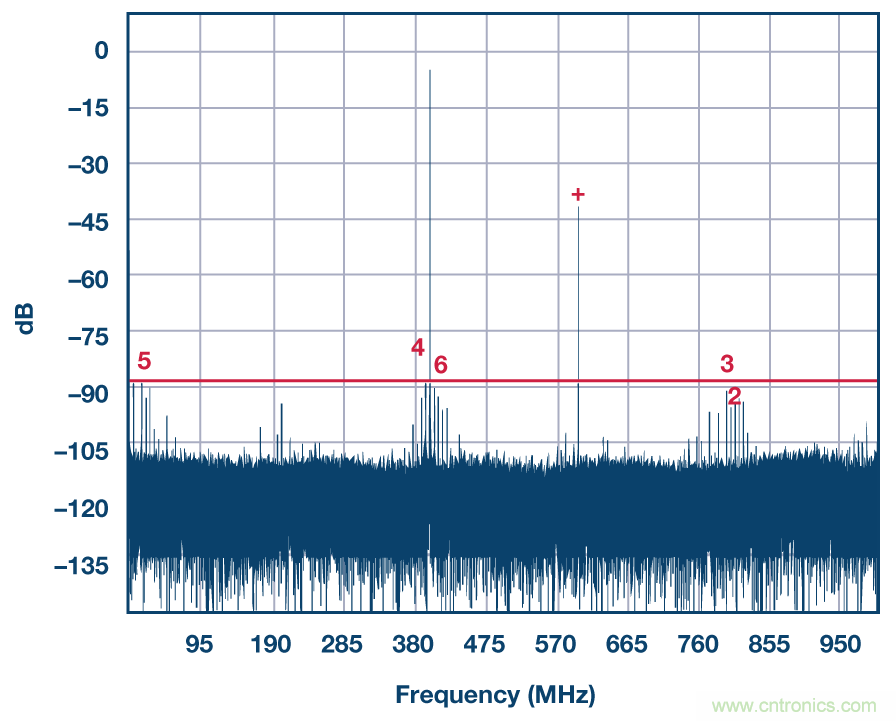

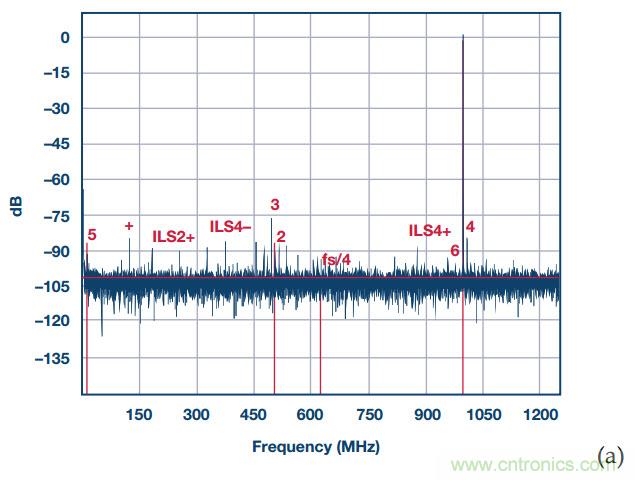

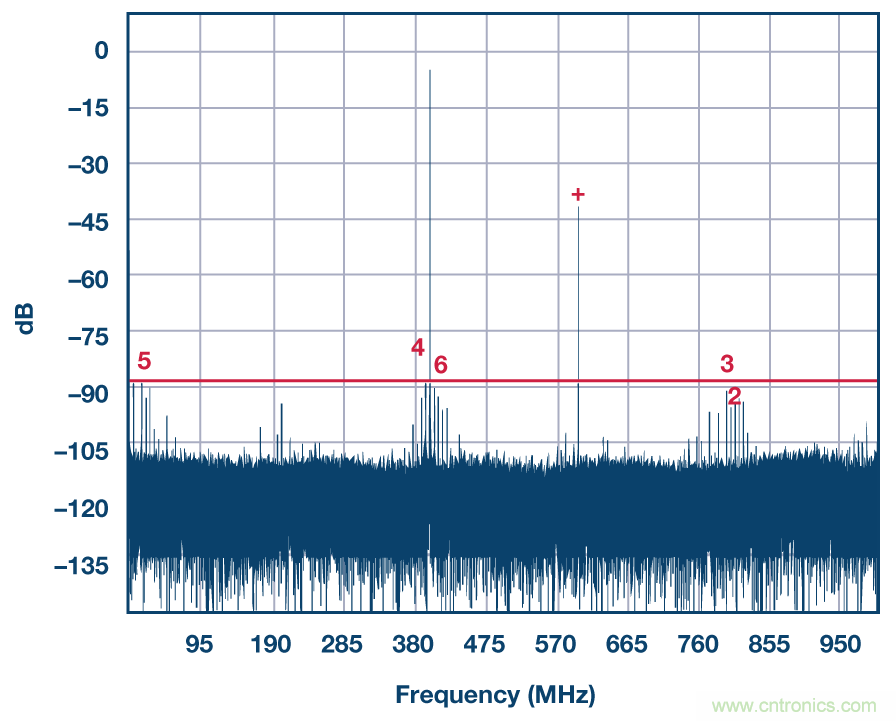

采用乒乓方案并且無(wú)任何通道失配校正的一個(gè)示例,以及其產(chǎn)生的交錯(cuò)雜散見(jiàn)圖3���。在該例中���,兩個(gè)雙通道14位/1 GSPS ADC AD9680以交替乘以正弦波的速率進(jìn)行采樣,從而返回單個(gè)組合輸出數(shù)據(jù)流���,速率為2 GSPS���。當(dāng)我們查看該乒乓方案輸出頻譜的第一奈奎斯特頻段時(shí)(位于直流和1 GHz之間)�,可以看到輸入音�����,它是fIN = 400 MHz時(shí)位于左側(cè)的強(qiáng)音�;我們還能看到在fs/2 – fIN = 2G/2 – 400 M = 600 MHz處有較強(qiáng)的增益/時(shí)序失配雜散。由于通道本身的失真以及其它損害�,我們還能看到一系列其它信號(hào)音,但都低于–90 dB線���。

圖3. 乒乓方案的2 GSPS輸出數(shù)據(jù)組合頻譜�����,采用兩個(gè)AD9680在1 GSPS時(shí)鐘下獲取,采樣相移為180°���。

更高次交錯(cuò)

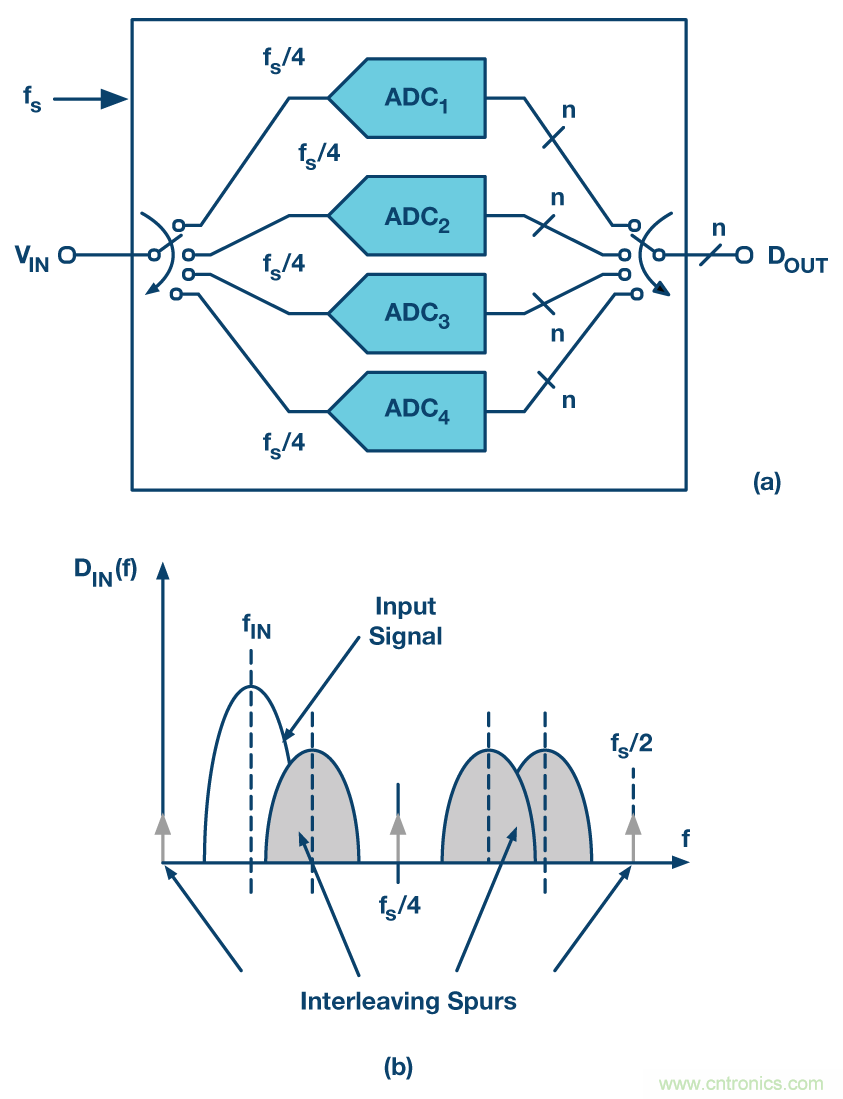

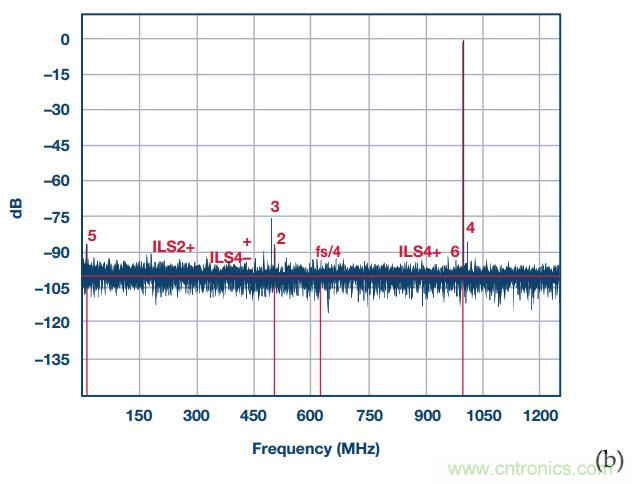

當(dāng)具有兩個(gè)以上通道時(shí)����,上文所說(shuō)的頻率規(guī)劃就不那么實(shí)用了�。我們無(wú)法將交錯(cuò)雜散的位置限定在奈奎斯特頻段的某一小部分。比如考慮四路交錯(cuò)ADC的情況��,如圖4 (a)所示。此時(shí)�,失調(diào)失配會(huì)提高直流、fs/4和fs/2時(shí)的信號(hào)音����,而增益和時(shí)序交錯(cuò)鏡像位于fs/4 – fIN、fs/4 + fIN和fs/2 – fIN��。交錯(cuò)ADC輸出頻譜的一個(gè)示例請(qǐng)參見(jiàn)圖4 (b)�����。很明顯���,除非輸入位于fs/8以內(nèi)的帶寬之內(nèi)��,否則無(wú)論fIN的位置如何��,輸入都會(huì)與部分交錯(cuò)雜散重疊����,并且如果輸入是一個(gè)極端窄帶信號(hào)�,那么我們不應(yīng)當(dāng)嘗試使用寬帶交錯(cuò)ADC將其數(shù)字化。

在這種情況下���,我們需要最大程度降低IL雜散功率�����,以便獲得完整的奈奎斯特頻譜和更干凈的頻譜��。為了達(dá)到這個(gè)目的�����,我們使用校準(zhǔn)技術(shù)來(lái)補(bǔ)償通道間失配�。校正失配的影響后,最終的IL雜散功率會(huì)下降��。SFDR和SNR都會(huì)得益于該雜散功率的下降��。

補(bǔ)償方法受限于失配可測(cè)量并最終校正的精度�����。除了校準(zhǔn)所能達(dá)到的水平外����,為了進(jìn)一步抑制殘留雜散�����,還可間歇性隨機(jī)打亂通道輸入采樣的順序。這樣做之后��,前面討論的由于未校準(zhǔn)失配而產(chǎn)生的轉(zhuǎn)換輸入信號(hào)調(diào)制效果將從固定碼噪聲轉(zhuǎn)換為偽隨機(jī)噪聲�����。因此�,IL音和干擾周期碼轉(zhuǎn)換為偽隨機(jī)噪聲類成分,并疊加至轉(zhuǎn)換器量化噪底而消失�����,或者至少將干擾雜散鏡像和信號(hào)音加以擴(kuò)散�。此時(shí),與IL雜散成分有關(guān)的功率疊加至噪底功率�����。因此�,雖然改善了失真,但SNR可能下降�,下降量為IL雜散功率加上噪聲。SNDR (SINAD)基本上沒(méi)有變化,因?yàn)樗墒д?��、噪聲和隨機(jī)化組成�����;它只是將IL貢獻(xiàn)因素從一個(gè)成分(失真)轉(zhuǎn)移到另一個(gè)成分(噪聲)���。

圖4. (a)四路交錯(cuò)ADC (b)對(duì)應(yīng)顯示交錯(cuò)雜散的第一奈奎斯特輸出頻譜

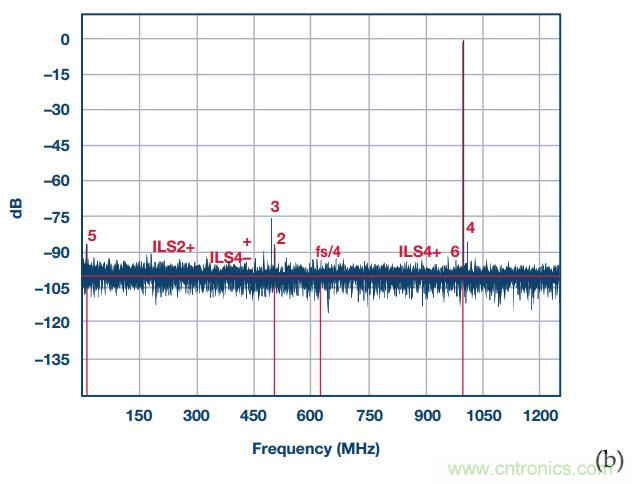

讓我們來(lái)看幾個(gè)交錯(cuò)ADC的示例。AD9625是一個(gè)12位/2.5 GSPS三路交錯(cuò)ADC�����。對(duì)三個(gè)通道之間的失配進(jìn)行校準(zhǔn)��,以便最大程度減少交錯(cuò)雜散���。圖5 (a)所示是一個(gè)輸入接近1 GHz的輸出頻譜示例���。在該頻譜中,除了約為1 GHz的輸入音外����,還可以看到通道在500 MHz附近存在2次和3次諧波失真,并在基頻處存在4次諧波失真���。交錯(cuò)失配校準(zhǔn)可大幅降低交錯(cuò)雜散的功耗�,并且在整個(gè)頻譜中可以看到大量的額外殘留的較小雜散音��。

為了進(jìn)一步減少這些殘留雜散成分�����,引入了通道隨機(jī)化���。加入了第四個(gè)校準(zhǔn)通道�����,然后將四個(gè)通道變?yōu)槿方诲e(cuò)���,并通過(guò)間歇性將交錯(cuò)通道與第四個(gè)更換,實(shí)現(xiàn)隨機(jī)改變順序���。這就好比人們可以像耍雜技那樣將三根柱子投向空中�����,然后每一次都更換第四根�����。這樣做之后����,可使殘留交錯(cuò)雜散功率隨機(jī)化,然后擴(kuò)散到噪底�。如圖5 (b)所示,經(jīng)過(guò)通道隨機(jī)化之后�����,交錯(cuò)雜散幾乎消失了�,而噪聲功率卻只略為增加,因而SNR降低2 dB�����。當(dāng)然����,需要注意的是,雖然圖5 (b)中的第二個(gè)頻譜比失真音遠(yuǎn)為干凈����,但隨機(jī)無(wú)法影響2次���、3次和4次諧波���,因?yàn)檫@些諧波不是交錯(cuò)雜散�。

圖5. AD9625的輸出頻譜�����,時(shí)鐘為2.5 GSPS���,輸入音接近1 GHz��。(a)順序三路交錯(cuò)�����;SNR = 60 dBFS�����,SFDR = 72 dBc����,受限于3次諧波,接近500 MHz���;然而�,整個(gè)頻譜中可見(jiàn)大量交錯(cuò)雜散�。(b)三路交錯(cuò),隨機(jī)通道置亂����;SNR = 58 dBFS,而SFDR = 72 dBc依然由3次諧波決定�,通過(guò)將功率擴(kuò)散到噪底而消除了所有交錯(cuò)雜散。

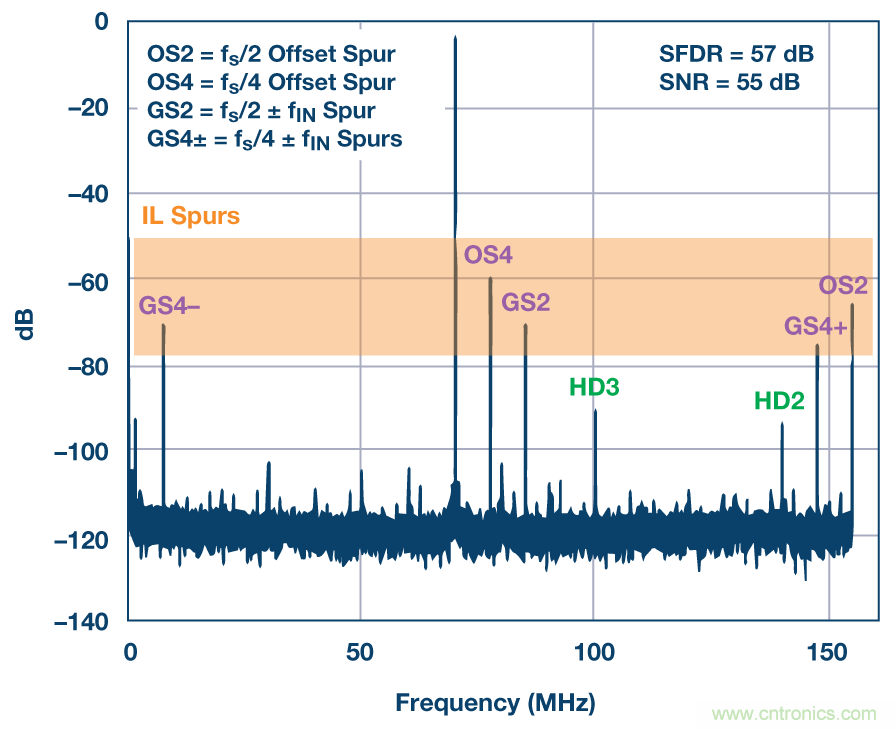

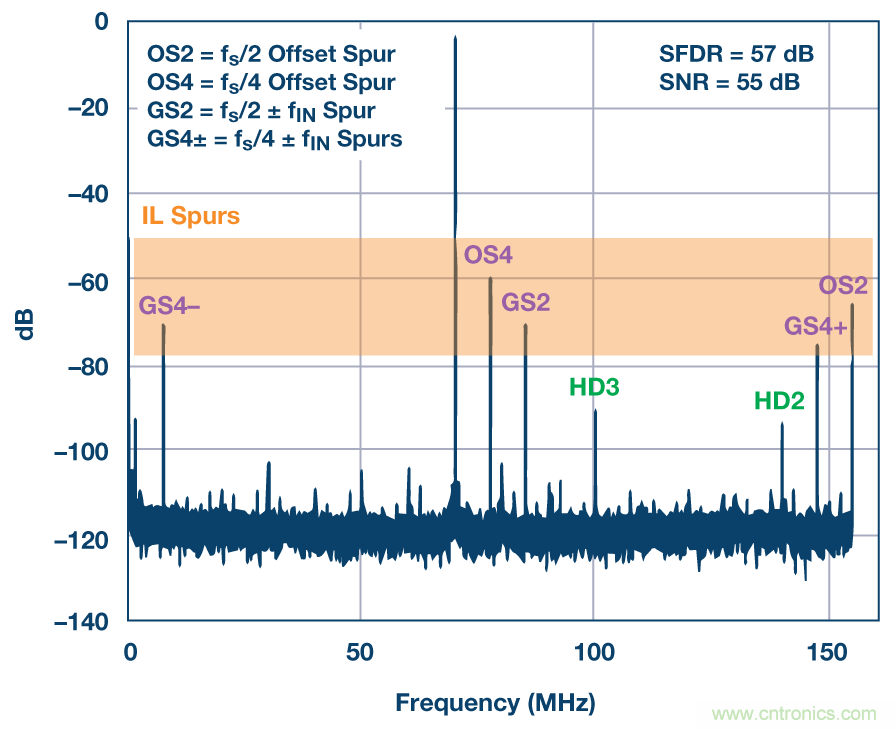

使用通道隨機(jī)化的另一個(gè)交錯(cuò)ADC示例如圖6中的頻譜所示���。此時(shí)采用四路交錯(cuò)16位/310 MSPS ADC AD9652����。圖6示例中�����,四個(gè)通道以固定順序交錯(cuò)�����,并且不進(jìn)行任何減少通道失配的校準(zhǔn)。頻譜清楚表明交錯(cuò)雜散位于預(yù)計(jì)頻率位置���,且它們的大功率遠(yuǎn)高于2次和3次諧波��,并將無(wú)雜散動(dòng)態(tài)范圍限制為僅有57 dBc。

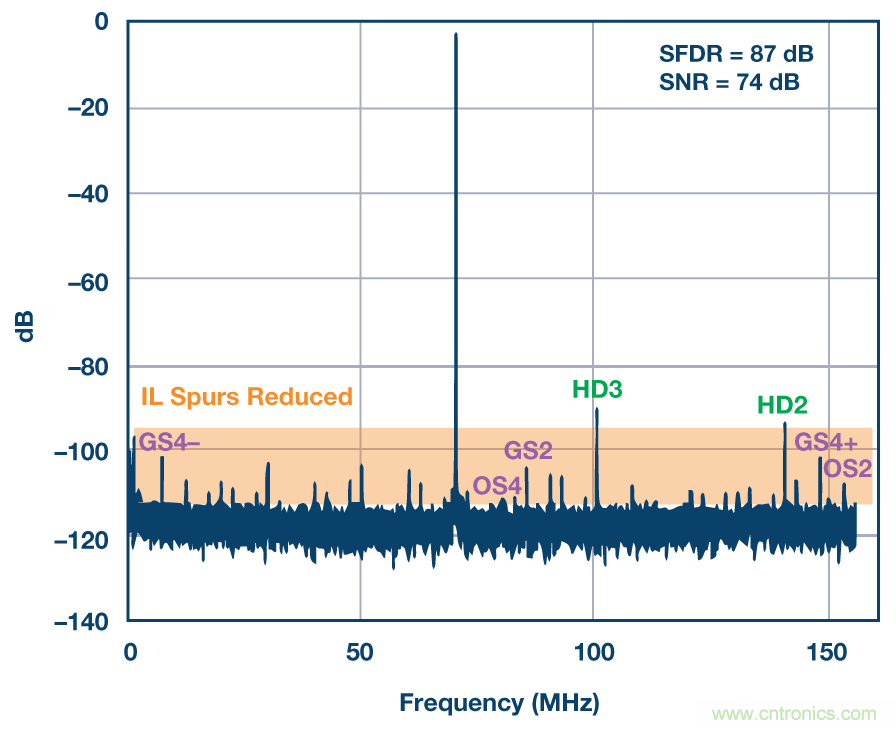

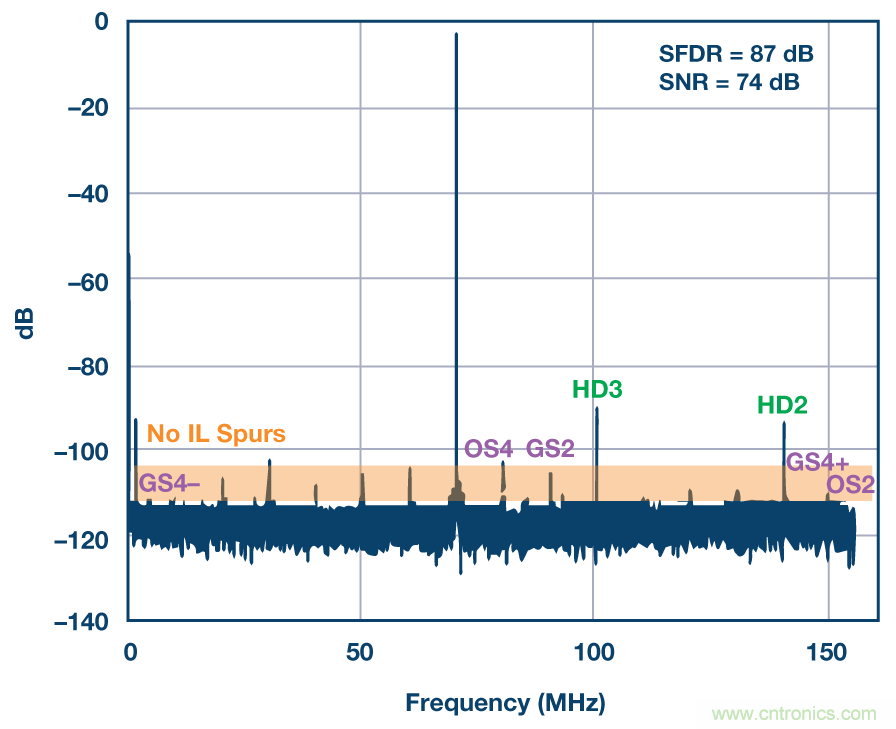

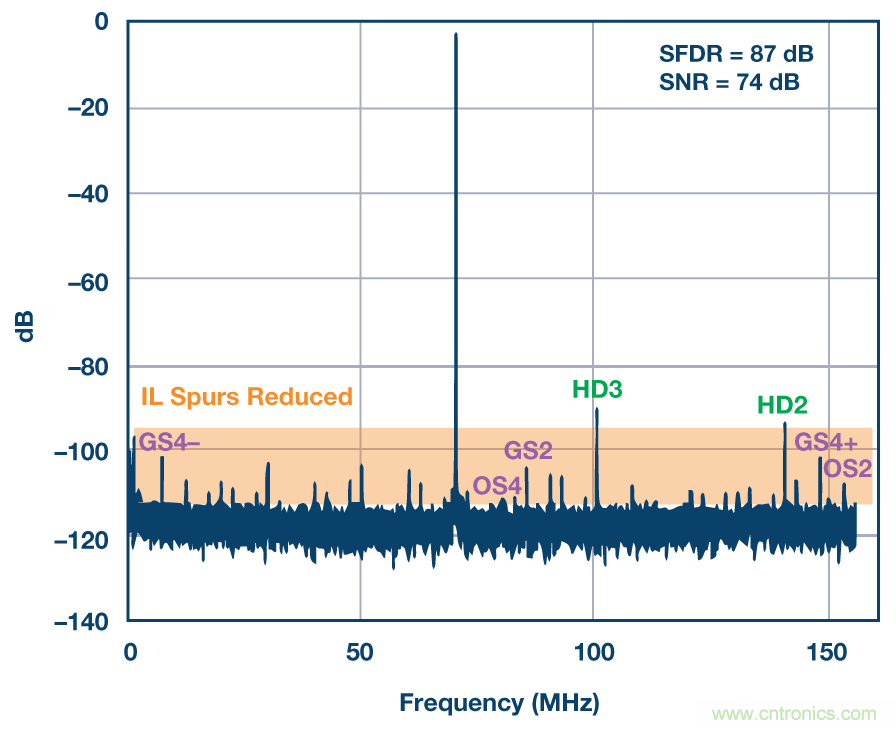

然而����,如果同樣的ADC經(jīng)過(guò)前景校準(zhǔn)以便減少通道失配,那么交錯(cuò)雜散功率將會(huì)大幅下降��,如圖7所示����。與上例中的情況類似,通道諧波失真不受影響���,但通過(guò)通道失配校準(zhǔn)大幅降低了交錯(cuò)雜散功率��。

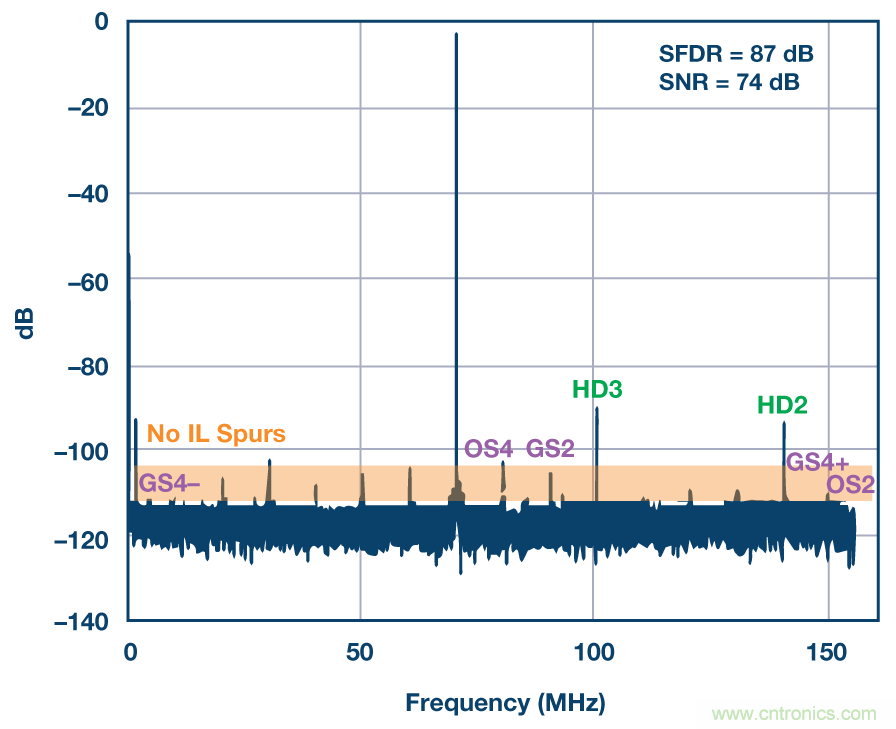

最后��,圖7中的頻譜純度可得到進(jìn)一步改善���,方法是使通道順序隨機(jī)化���,如圖8所示。此時(shí)���,隨機(jī)化使用專利技術(shù)�����,對(duì)四個(gè)通道的順序進(jìn)行間歇性加擾無(wú)需通過(guò)另一個(gè)(第五個(gè))通道來(lái)達(dá)成�����,從而省下了與此相關(guān)的功耗��。如圖8所示�����,經(jīng)過(guò)隨機(jī)化之后��,結(jié)果頻譜中僅有常規(guī)諧波失真����。

圖6. AD9652的輸出頻譜,時(shí)鐘為 fs=310 MHz�����,采用fIN ~70 MHz的正弦輸入����。此時(shí),未施加通道校準(zhǔn)和隨機(jī)化����。2次(HD2)和混疊3次(HD3)諧波分別在大約140 MHz和100 MHz處可見(jiàn)���。交錯(cuò)(IL)雜散同樣可見(jiàn)���。這些是直流、fs/2(圖中的OS2)以及fs/4(圖中的OS4)處的失調(diào)音�����。另外��,增益(時(shí)序)雜散可見(jiàn)于fs /2-fIN(圖中的GS2)����、fs /4+fIN(圖中的GS4+)以及fs /4- fIN(圖中的GS4-)��。此圖中的SNR查詢?nèi)藶樽儾盍?����,因?yàn)椴糠蛛s散成分和噪聲功率混在了一起�。

圖7. 同一個(gè)AD9652的輸出頻譜�����,采用同樣的輸入����,但經(jīng)過(guò)校準(zhǔn)后四個(gè)通道減少了失配。與圖6相比�,雖然2次和3次諧波未受影響,但交錯(cuò)雜散的功率大幅下降��,并且SFDR改善了30 dB��,即從57 dBc到87 dBc�。

圖8. 上例開(kāi)啟交錯(cuò)順序隨機(jī)化之后的輸出頻譜。隨機(jī)化殘留交錯(cuò)雜散可將它們的功率擴(kuò)散到噪底中,相應(yīng)的尖峰便消失了���?����?梢钥吹降膬H有常規(guī)諧波失真���。SNR幾乎未受影響,因?yàn)閬?lái)自交錯(cuò)音并擴(kuò)散的雜散功率經(jīng)過(guò)失配校準(zhǔn)后可以忽略��。

結(jié)論

時(shí)間交錯(cuò)是增加數(shù)據(jù)轉(zhuǎn)換器帶寬的強(qiáng)大技術(shù)�����。最近在失配校準(zhǔn)方面���,以及通過(guò)隨機(jī)化技術(shù)消除殘留雜散成分方面的發(fā)展已經(jīng)能夠?qū)崿F(xiàn)完全集成、極高速12/14/16位交錯(cuò)ADC���。

在輸入信號(hào)受頻帶限制的情況下(比如很多通信應(yīng)用)�,乒乓(雙路)交錯(cuò)方法可通過(guò)頻率規(guī)劃將干擾交錯(cuò)雜散分配到遠(yuǎn)離目標(biāo)輸入頻段的位置���。然后便可以數(shù)字手段過(guò)濾雜散成分��。雖然這種方法相比工作在IL采樣速率一半的非交錯(cuò)式ADC獲得同樣的無(wú)雜散輸入帶寬所需的功耗要高出幾乎一倍���,但它不僅可以通過(guò)處理增益提高動(dòng)態(tài)范圍3 dB�,而且還能降低抗混疊的滾降�,并修平ADC前的濾波器——因?yàn)镮L采樣速率高。

若需要用到IL轉(zhuǎn)換器的全部輸入頻帶才能捕捉寬帶輸入信號(hào)����,那么可以采用更高次的交錯(cuò)轉(zhuǎn)換器。這種情況下�����,校準(zhǔn)和隨機(jī)置亂可實(shí)現(xiàn)交錯(cuò)失真和雜散成分的補(bǔ)償和消除��。

Endnotes

[1] 雖然此處僅討論了模數(shù)轉(zhuǎn)換器�,但所有原理同樣適用于數(shù)模轉(zhuǎn)換器的時(shí)間交錯(cuò)特性。.

[2] 請(qǐng)注意�,重要的是增益誤差不匹配,而不是絕對(duì)值��。因?yàn)槿绻麅蓚€(gè)通道具有相同的增益(誤差)�,則G1 = G2���。 這種情況下,兩個(gè)通道均同樣擴(kuò)大����,從而將兩個(gè)數(shù)據(jù)流重新整合到單一DOUT數(shù)據(jù)流中,而無(wú)需幅度(或調(diào)制)交替�����,且未引入增益雜散��。

[3]一般而言���,對(duì)于M通道交錯(cuò)���,fOS = (k/M) fS時(shí)會(huì)出現(xiàn)失調(diào)雜散,其中k = 0���、1�、2... (Manganaro, 2011年)����。

[4]一般而言,對(duì)于M通道交錯(cuò)���,fGS = ± fIN + (k/M) fS時(shí)會(huì)出現(xiàn)增益和時(shí)序偏斜圖像����,其中k = 1����、2... (Manganaro, 2011年)。

參考電路

Beavers, Ian. “千兆采樣ADC通過(guò)快速運(yùn)行應(yīng)對(duì)新挑戰(zhàn)”,ADI公司�,2014年。

Black, William and David Hodges. “時(shí)間交錯(cuò)轉(zhuǎn)換器陣列” IEEE Journal of Solid-State Circuit,第SC-15卷第6期��,1980年����。

Bosworth, Duncan. “GSPS數(shù)據(jù)轉(zhuǎn)換器拯救電子監(jiān)控與對(duì)抗系統(tǒng)。”, ADI公司���,2014年��。

Elbornsson, Jonas, Fredrik Gustafsson, 和 Jan-Erik Eklund. “分析隨機(jī)交錯(cuò)ADC系統(tǒng)中的失配影響” IEEE Transactions on Circuits and Systems, 第52卷第3期����,2005年。

Harris, Jonathan. “深入了解交錯(cuò)式ADC的本質(zhì).” EDN Network, 2013年.

Harris, Jonathan. “交錯(cuò)式ADC入門(mén)” EDN Network, 2013.

Manganaro, Gabriele. Advanced Data Converters. Cambridge, UK: Cambridge University Press, 2011.

推薦閱讀: