【導(dǎo)讀】精密信號鏈設(shè)計人員面臨著滿足中等帶寬應(yīng)用中噪聲性能要求的挑戰(zhàn),最后往往要在噪聲性能和精度之間做出權(quán)衡??s短上市時間并在第一時間完成正確的設(shè)計則進(jìn)一步增加了壓力。持續(xù)時間Σ-Δ (CTSD) ADC本身具有架構(gòu)優(yōu)勢,簡化了信號鏈設(shè)計,從而縮減了解決方案尺寸,有助于客戶縮短終端產(chǎn)品的上市時間。為了說明CTSD ADC本身的架構(gòu)優(yōu)勢及其如何適用于各種精密中等帶寬應(yīng)用,我們將深入分析信號鏈設(shè)計,讓設(shè)計人員了解CTSD技術(shù)的關(guān)鍵優(yōu)勢,并探索AD4134 精密ADC易于設(shè)計的特性。

簡介

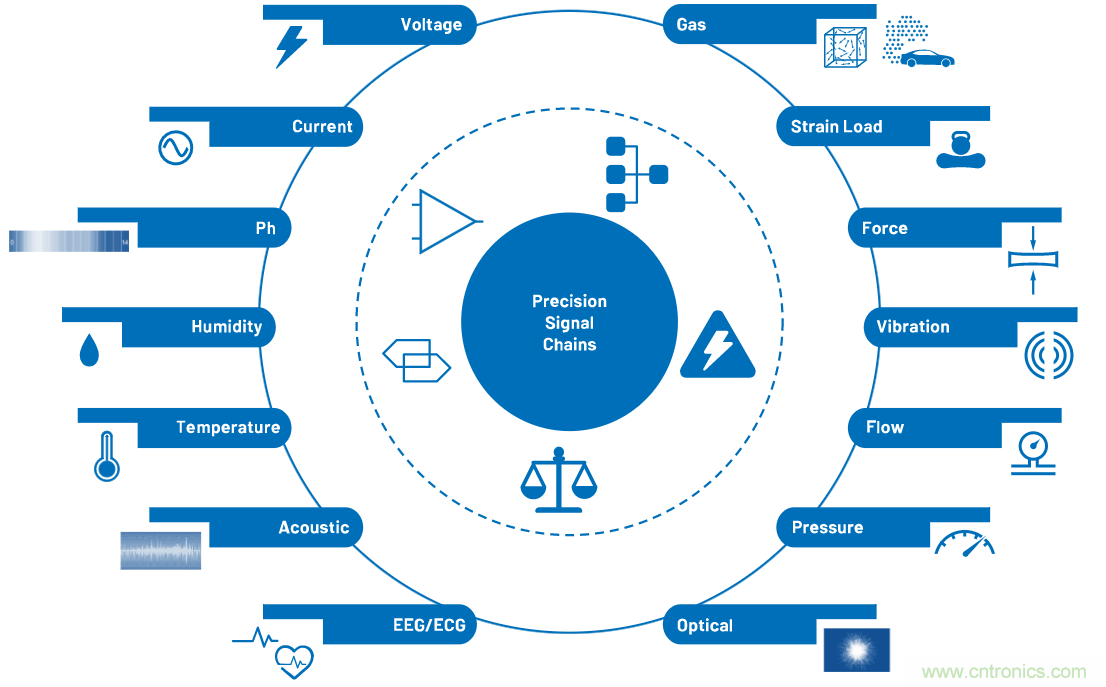

在許多數(shù)字處理應(yīng)用和算法中,在過去的20年里,日益要求所有轉(zhuǎn)換器技術(shù)都具有更高的分辨率和精度。通過使用外部數(shù)字控制器,借助平均和優(yōu)化的濾波方案等軟件技術(shù)可提取并提供更精確的結(jié)果,從而提高ADC受限的分辨率/精度。為了減少數(shù)字微控制器或DSP的大量后處理工作,設(shè)計人員可使用高性能精密ADC。這將減少數(shù)字方面的優(yōu)化時間,也可以考慮使用成本較低的微控制器或DSP。精密ADC的應(yīng)用和市場很廣泛:

● 工業(yè)儀器儀表:振動分析、溫度/壓力/應(yīng)力/流量測量、動態(tài)信號分析、聲學(xué)分析

● 醫(yī)療儀器儀表:電生理學(xué)、血液分析、心電圖(EKG/ECG)

● 防務(wù)應(yīng)用:聲納、遙測

● 測試和測量:音頻測試、硬件循環(huán)、電能質(zhì)量分析

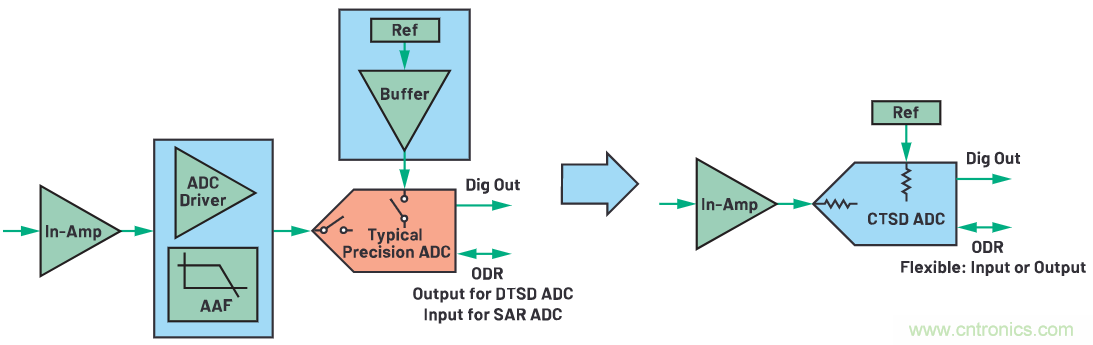

圖1.精密ADC信號鏈?zhǔn)纠?/div>

由ADC處理的模擬輸入信號可以是帶有電壓、電流輸出的傳感器信號,也可以是帶寬范圍從直流到幾百kHz的反饋控制環(huán)路信號。ADC數(shù)字輸出格式和速率取決于以下數(shù)字控制器所需的應(yīng)用和后處理。一般而言,信號鏈設(shè)計人員遵循奈奎斯特采樣準(zhǔn)則,將數(shù)字控制器的ADC輸出數(shù)據(jù)速率(ODR)設(shè)置為至少是輸入頻率的兩倍。大多數(shù)ADC允許基于相關(guān)信號頻帶靈活地調(diào)整輸出數(shù)據(jù)速率。

對于目前可用的ADC,在ADC可與輸入信號交互前涉及到幾個信號調(diào)理階段。具有嚴(yán)格要求的信號調(diào)理電路需要圍繞特定和單獨(dú)的ADC技術(shù)進(jìn)行設(shè)計和定制,確保能夠?qū)崿F(xiàn)ADC數(shù)據(jù)手冊的性能。選擇ADC后,信號鏈設(shè)計人員的工作并沒有結(jié)束。通常需要花費(fèi)大量時間和精力來設(shè)計外設(shè)并進(jìn)行調(diào)整。ADI公司的設(shè)計仿真工具和模型庫可為設(shè)計人員提供技術(shù)支持,幫助他們應(yīng)對設(shè)計挑戰(zhàn)。

新方法:利用CTSD架構(gòu)簡化設(shè)計之旅

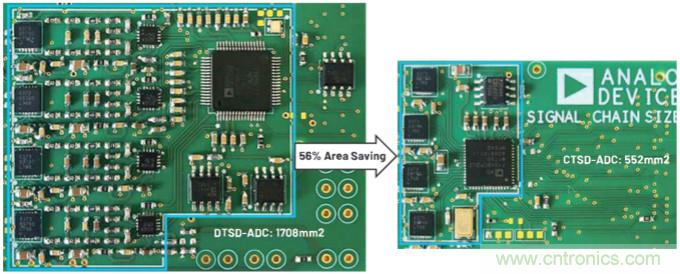

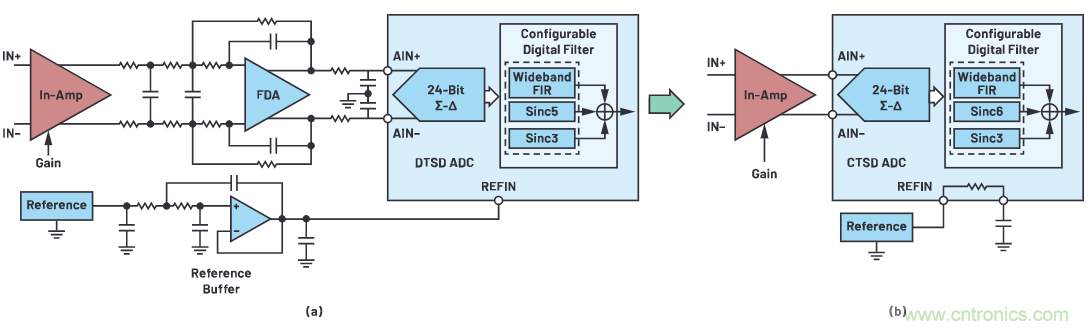

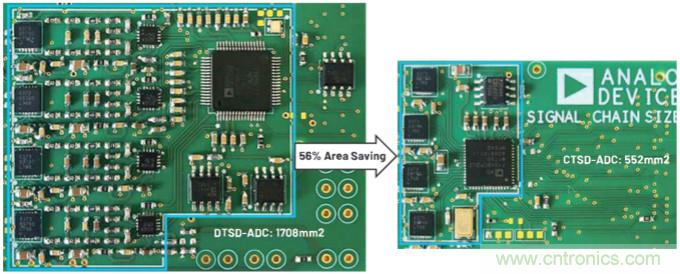

CTSD架構(gòu)主要用于音頻和高速ADC,現(xiàn)在針對精密應(yīng)用量身定制,可實(shí)現(xiàn)高精度,同時利用其獨(dú)特信號鏈簡化特性。利用此架構(gòu)可以減輕設(shè)計外設(shè)的工作量。圖2顯示了如何通過使用這種新的解決方案來實(shí)現(xiàn)高通道密度,將當(dāng)前ADC信號鏈簡化并縮減56%,圖中只是其中的一小部分。

圖2.具有ADI易于使用的新CTSD ADC的小尺寸解決方案。

為了說明CTSD ADC技術(shù)如何簡化信號鏈設(shè)計,本文重點(diǎn)介紹一般應(yīng)用的現(xiàn)有信號鏈中涉及的一些關(guān)鍵挑戰(zhàn),并演示了CTSD ADC如何緩解這些挑戰(zhàn)。

因此,我們首先介紹現(xiàn)有信號鏈中涉及的幾個設(shè)計步驟,第一個任務(wù)是選擇適合目標(biāo)應(yīng)用的正確ADC。

第1步:選擇ADC

除了應(yīng)用所需的最終數(shù)字輸出的分辨率和精度外,從廣泛的可用范圍中選擇合適的ADC時,信號帶寬、ODR、信號類型和要處理的范圍也是重要考慮因素。一般而言,在大多數(shù)應(yīng)用中,數(shù)字控制器要求使用算法來處理輸入信號的幅度、相位或頻率。

為了準(zhǔn)確地測量前面的任何一個因素,需要盡量減小數(shù)字化過程中增加的誤差。表1中詳細(xì)列出了主要誤差及其相應(yīng)的測量術(shù)語, 數(shù)據(jù)轉(zhuǎn)換基本指南中提供了進(jìn)一步詳細(xì)說明。

表1.ADC誤差和性能指標(biāo)

表1中的性能指標(biāo)與信號幅度和頻率有關(guān),通常稱為交流性能參數(shù)。

對于直流或近直流應(yīng)用,如處理50 Hz至60 Hz輸入信號的功率計量,必須考慮偏置、增益、INL和閃爍噪聲等ADC誤差。這些直流性能參數(shù)也需要針對應(yīng)用預(yù)期用途具有一定的溫度穩(wěn)定性。

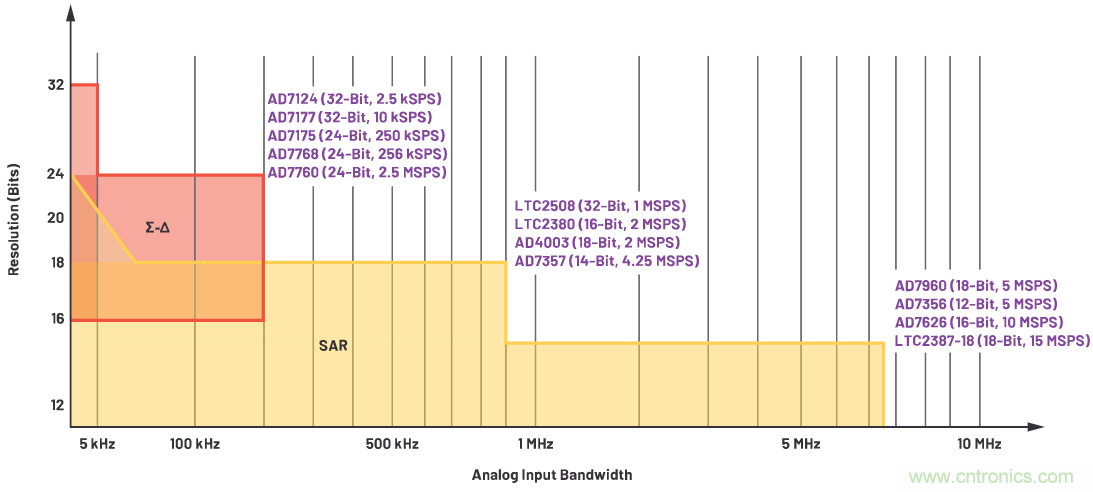

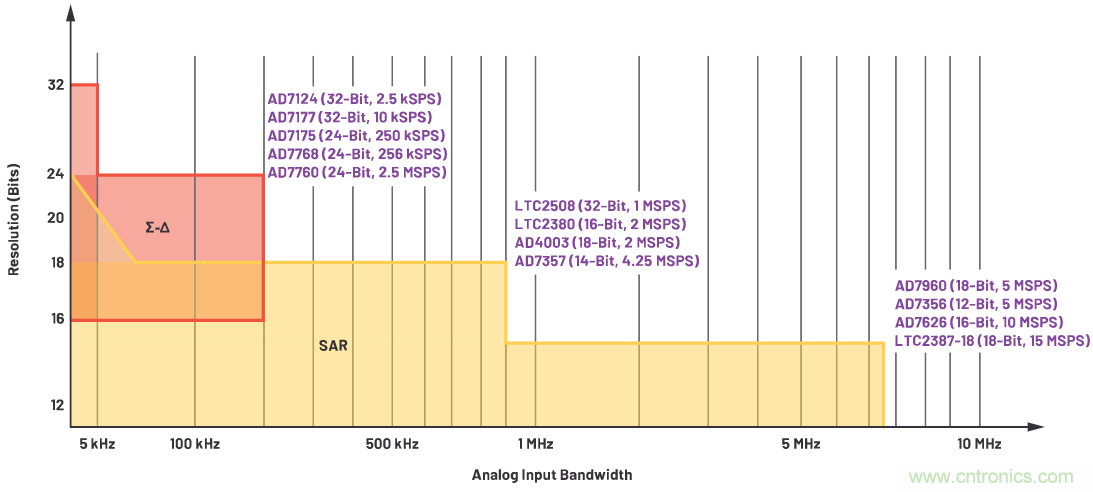

ADI提供各種行業(yè)領(lǐng)先的高性能ADC,以滿足多個應(yīng)用的系統(tǒng)需求,例如基于精度、速度或有限功耗預(yù)算的應(yīng)用。僅比較兩組ADC規(guī)格不足以正確選擇ADC。還必須考慮整體系統(tǒng)性能和設(shè)計挑戰(zhàn),這才是選擇ADC技術(shù)或架構(gòu)的關(guān)鍵所在。傳統(tǒng)上首選兩大類ADC架構(gòu)。常用的是 逐次逼近寄存器 (SAR) ADC,其遵循簡單的奈奎斯特準(zhǔn)則。它指出,如果以其頻率的兩倍采樣,可重構(gòu)信號。SAR ADC的優(yōu)勢在于出色的直流性能、小尺寸、低延遲以及通過ODR進(jìn)行功耗調(diào)節(jié)。

第二種技術(shù)選項(xiàng)是離散時間Σ-Δ (DTSD) ADC,其工作原理是樣本數(shù)目越大,丟失的信息就越少。因此,采樣頻率遠(yuǎn)高于規(guī)定的奈奎斯特頻率,這種方案稱為過采樣。此架構(gòu)還有一個優(yōu)勢是,由于采樣而增加的誤差可在目標(biāo)頻帶內(nèi)最小化。因此,DTSD ADC兼具出色的直流和交流性能,但延遲較高。

圖3展示了SAR和DTSD ADC的典型模擬輸入帶寬,以及一些不同速度和分辨率的常用產(chǎn)品選擇。也可使用精密快速搜索功能 幫助您選擇ADC。

圖3.精密ADC架構(gòu)定位。

此外,現(xiàn)在還有一種新型精密ADC可用。這些ADC基于DTSD ADC,與DTSD ADC性能相當(dāng),但在簡化整個信號鏈設(shè)計過程方面具有獨(dú)特的優(yōu)勢。這個全新的ADC系列可以解決現(xiàn)有信號鏈后續(xù)幾個設(shè)計步驟中比較突出的挑戰(zhàn)。

第2步:輸入與ADC接口

由ADC處理其輸出的傳感器可能具有非常高的靈敏度。設(shè)計人員必須清楚地知道傳感器將與之接口的ADC輸入結(jié)構(gòu),確保ADC誤差不會影響實(shí)際傳感器信號或使其失真。

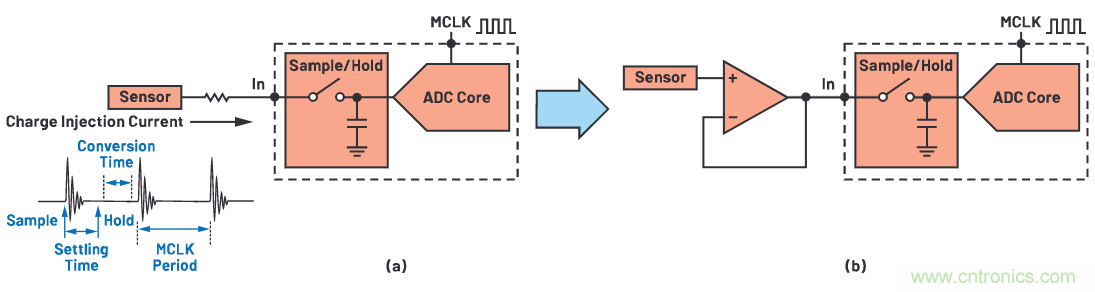

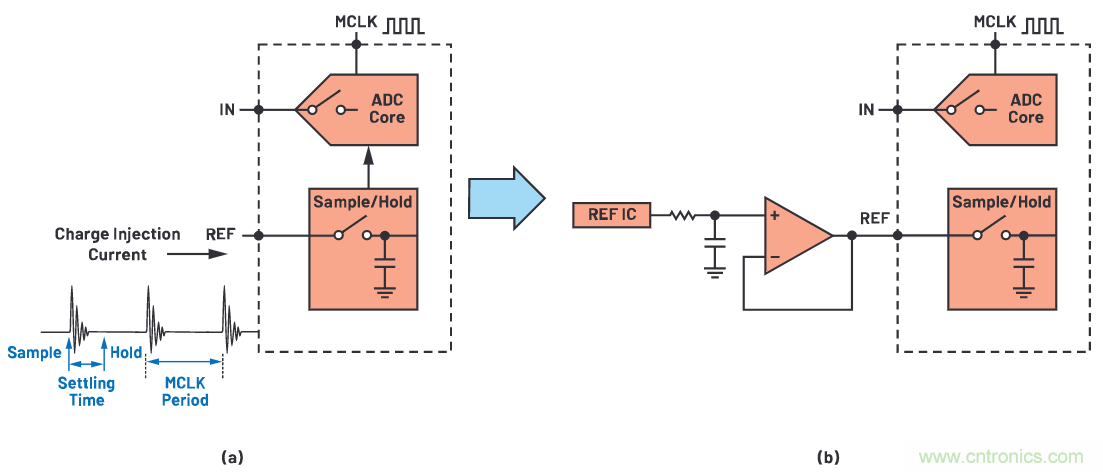

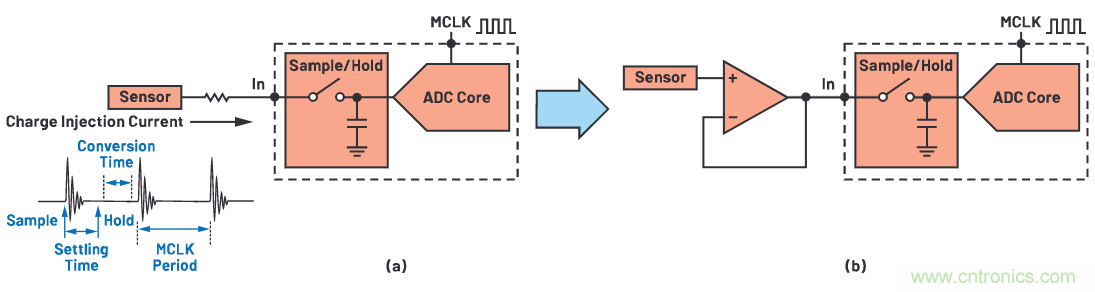

在傳統(tǒng)SAR、DTSD ADC中,輸入結(jié)構(gòu)稱為開關(guān)電容采樣保持電路,如圖4所示。在每個采樣時鐘邊緣,當(dāng)采樣開關(guān)改變其ON/OFF狀態(tài)時,需要支持有限電流需求,以便將保持電容充放電至一個新的采樣輸入值。此電流需要通過輸入源提供,在我們討論的示例中,這個輸入源是傳感器。此外,開關(guān)本身有一些片內(nèi)寄生電容,會將一些電荷注入電源,稱為電荷注入反沖。由此增加的誤差源也需要由傳感器吸收,以免對傳感器信號造成不利影響。

圖4.(a)開關(guān)電容電荷注入反沖到傳感器,(b)使用輸入緩沖器隔離反沖效應(yīng)。

大多數(shù)傳感器無法提供這種電流幅度,表明它們不能直接驅(qū)動開關(guān)電路。在另一種情況下,即使傳感器能夠支持這些電流需求,傳感器的有限阻抗也會在ADC輸入端增加誤差。電荷注入電流與輸入成函數(shù)關(guān)系,此電流將會在傳感器阻抗上引起與輸入相關(guān)的壓降。如圖4a所示,ADC的輸入錯誤。在傳感器和ADC之間放置一個驅(qū)動放大器可以解決這些問題,如圖4b所示。

現(xiàn)在我們需要為此放大器設(shè)定標(biāo)準(zhǔn)。首先,放大器應(yīng)支持充電電流并能夠吸收電荷注入反沖。其次,該放大器的輸出需要在采樣邊緣的末端完全穩(wěn)定,使得對ADC輸入采樣時不會增加誤差。這意味著放大器應(yīng)能提供瞬時電流階躍,映射為具有高壓擺率,并對這些瞬態(tài)事件提供快速建立響應(yīng),映射為具有高帶寬。隨著ADC的采樣頻率和分辨率的增加,能否滿足這些需求變得至關(guān)重要。

設(shè)計人員,特別是處理中等帶寬應(yīng)用的設(shè)計人員所面臨的一大挑戰(zhàn)是為ADC確定合適的放大器。如前所述,ADI提供了一組仿真模型和精密ADC驅(qū)動器工具來簡化此步驟,但對于設(shè)計人員來說,這是實(shí)現(xiàn)ADC數(shù)據(jù)手冊性能的額外設(shè)計步驟。一些新時代的SAR和DTSD ADC通過使用新穎的采樣技術(shù)來完全降低瞬態(tài)電流需求,或采用集成放大器應(yīng)對這一挑戰(zhàn)。但這兩種解決方案都限制了信號帶寬的范圍或削弱了ADC的性能。

CTSD ADC的優(yōu)勢:CTSD ADC通過為易于驅(qū)動的電阻輸入而非開關(guān)電容輸入提供新的選項(xiàng),來解決這個問題。這表明對高帶寬、大壓擺率的放大器沒有硬性要求。如果傳感器可直接驅(qū)動此阻性負(fù)載,則可直接與CTSD ADC接口;否則可在傳感器和CTSD ADC之間連接任何低帶寬、低噪聲放大器。

第三步:基準(zhǔn)電壓源與ADC接口

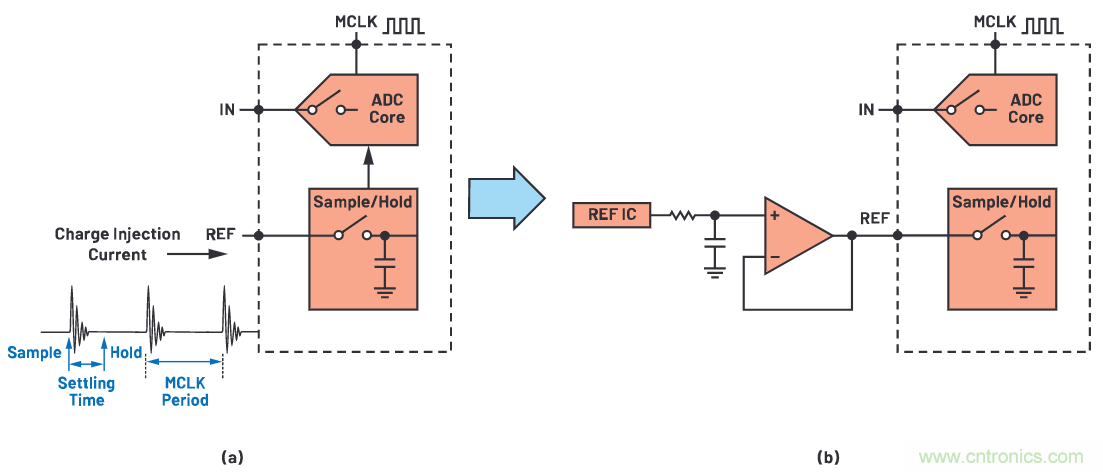

與基準(zhǔn)電壓源接口涉及的挑戰(zhàn)與輸入接口類似。傳統(tǒng)ADC的基準(zhǔn)電壓源輸入也是開關(guān)電容。在每個采樣時鐘邊緣,基準(zhǔn)電壓源需要對內(nèi)部電容充電,因此需要具有良好建立時間的大開關(guān)電流。

可用的基準(zhǔn)電壓源IC不支持大開關(guān)電流需求,并且?guī)捰邢?。第二個接口挑戰(zhàn)是來自這些基準(zhǔn)電壓源的噪聲比ADC的噪聲大。為了濾除這種噪聲,使用了一階RC電路。一方面,我們限制基準(zhǔn)電壓源的帶寬以減少噪聲,另一方面,我們需要快速建立時間。這是兩個需要同時滿足的相反要求。因此,使用低噪聲緩沖器來驅(qū)動ADC基準(zhǔn)引腳,如圖5b所示。此緩沖器的壓擺率和帶寬基于ADC的采樣頻率和分辨率來決定。

同樣,與我們的精密輸入驅(qū)動器工具一樣,ADI也提供針對ADC仿真和選擇正確的基準(zhǔn)電壓源緩沖區(qū)的工具。與輸入一樣,一些新時代的SAR和DTSD ADC也提供集成基準(zhǔn)電壓源緩沖區(qū)選項(xiàng),但具有性能和帶寬限制。

圖5.(a)開關(guān)電容電荷注入反沖到基準(zhǔn)電壓源IC (b)使用基準(zhǔn)電壓源緩沖區(qū)隔離反沖效應(yīng)。

CTSD ADC的優(yōu)勢:使用CTSD ADC可完全跳過此設(shè)計步驟,因?yàn)樗鼮轵?qū)動阻性負(fù)載提供一種新的簡便選項(xiàng),而不需要此類高帶寬、大壓擺率的緩沖器。具有低通濾波器的基準(zhǔn)電壓源IC可直接與基準(zhǔn)引腳接口。

第四步:使信號鏈不受干擾影響

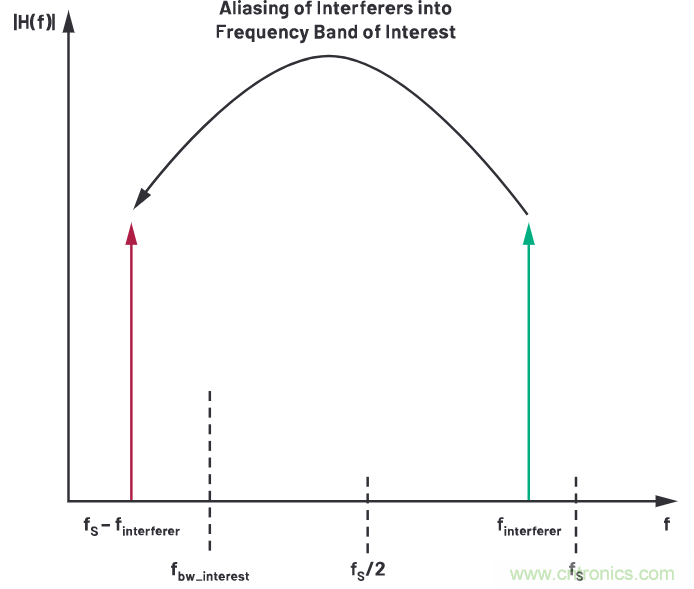

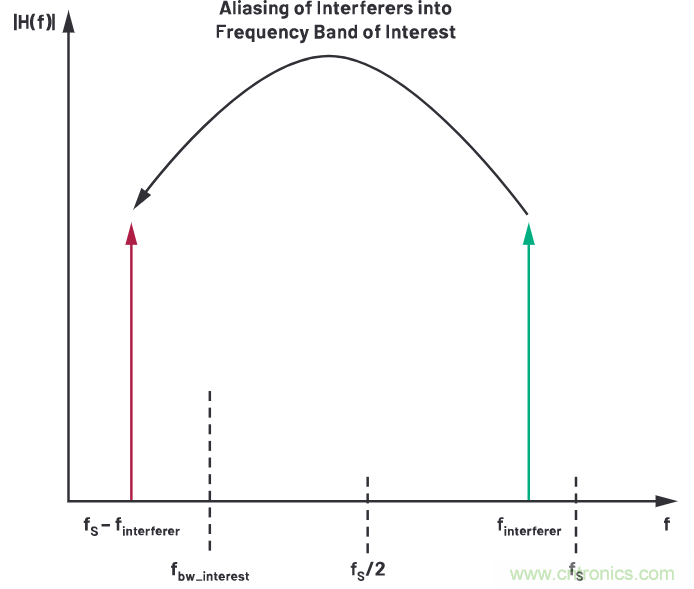

對連續(xù)信號進(jìn)行采樣和數(shù)字化處理會導(dǎo)致信息丟失,這稱為量化噪聲。采樣頻率和位數(shù)決定了ADC架構(gòu)的性能限制。解決基準(zhǔn)電壓源和輸入的性能和接口挑戰(zhàn)之后,下一個難題是解決高頻(HF)干擾源/噪聲折疊到目標(biāo)低頻帶寬的問題。這稱為混疊或折回。這些進(jìn)入目標(biāo)帶寬的高頻或帶外干擾源的反射圖像導(dǎo)致信噪比(SNR)降低。根據(jù)采樣準(zhǔn)則,采樣頻率周圍的任何信號音都會在帶內(nèi)折回,如圖6所示,在目標(biāo)頻帶內(nèi)產(chǎn)生不必要的信息或錯誤。有關(guān)混疊的更多詳細(xì)信息參見教程MT-002: 奈奎斯特準(zhǔn)則對數(shù)據(jù)采樣系統(tǒng)設(shè)計有何意義。

圖6.由于采樣使帶外干擾源混疊/折回進(jìn)入目標(biāo)頻帶。

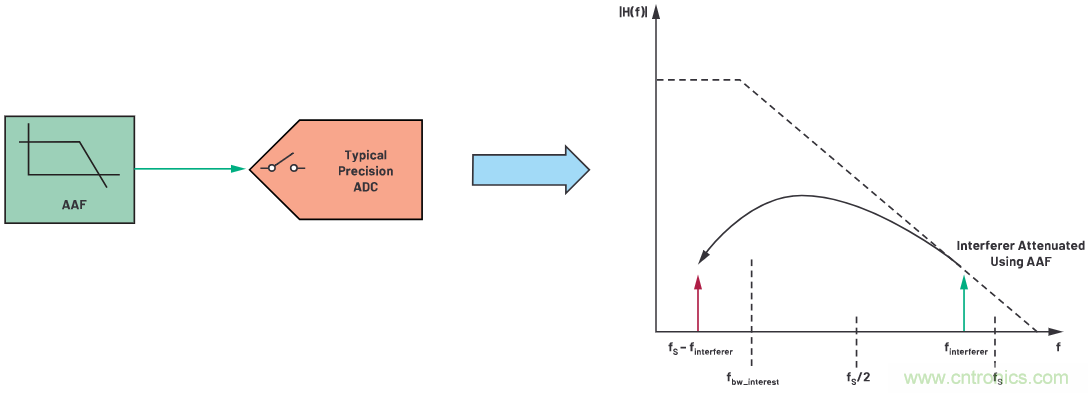

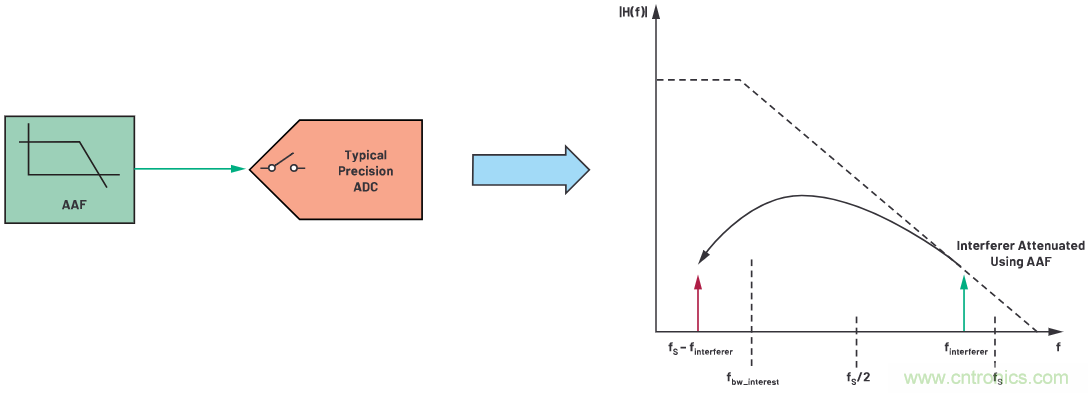

緩解折回效應(yīng)的一種解決方案是使用一種稱為抗混疊濾波器(AAF)的低通濾波器來衰減不必要的干擾源幅度,這樣當(dāng)衰減后的干擾源折回帶內(nèi)時,可以保持所需的信噪比。該低通濾波器通常集成有驅(qū)動器放大器,如圖7所示。

圖7.使用抗混疊濾波器緩解對帶內(nèi)性能造成的混疊效應(yīng)。

設(shè)計此放大器時,最大的挑戰(zhàn)是在快速建立和低通濾波要求之間尋求平衡。另一個挑戰(zhàn)是該解決方案需要針對每個應(yīng)用需求進(jìn)行微調(diào),這就對各個應(yīng)用采用單個平臺設(shè)計造成了限制。ADI有很多 抗混疊濾波器工具設(shè)計 ,可幫助設(shè)計人員克服此挑戰(zhàn)。

CTSD ADC的優(yōu)勢:這種抗擾性可由CTSD ADC本身具有的混疊抑制特性解決,這是CTSD ADC獨(dú)有的特性。采用這種技術(shù)的ADC不需要AAF。因此,我們有望直接將CTSD ADC輕松地連接到傳感器,向這個目標(biāo)又近了一步。

第五步:選擇ADC時鐘頻率和輸出數(shù)據(jù)速率

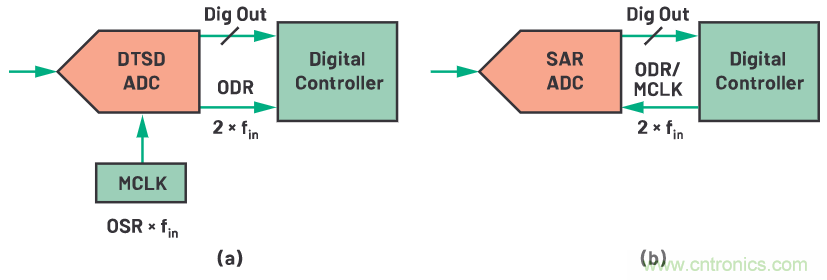

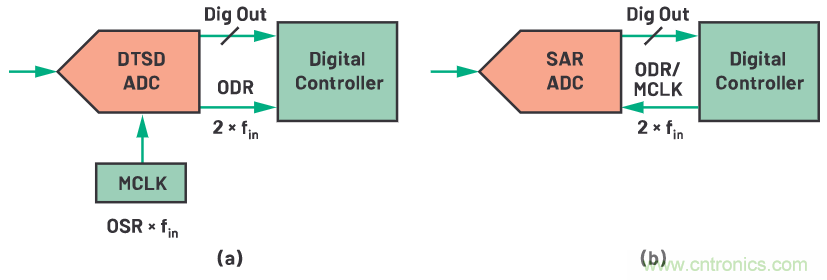

接下來,我們來討論兩種傳統(tǒng)ADC類型的時鐘要求。DTSD是過采樣的ADC,這是指ADC以高于奈奎斯特采樣速率進(jìn)行采樣的ADC。但是,將ADC過采樣數(shù)據(jù)直接提供給外部數(shù)字控制器,大量的冗余信息會使其過載。在過采樣系統(tǒng)中,核心ADC輸出使用片內(nèi)數(shù)字濾波器進(jìn)行抽取,使最終ADC數(shù)字輸出的數(shù)據(jù)速率更低,通常是信號頻率的兩倍。

對于DTSD ADC,設(shè)計人員需要計劃為核心ADC提供高頻采樣時鐘,并設(shè)定所需的輸出數(shù)據(jù)速率。ADC將在這個所需的ODR和ODR時鐘上提供最終數(shù)字輸出。數(shù)字控制器使用此ODR時鐘輸入數(shù)據(jù)。

接下來,我們解決SAR ADC的時鐘要求,通常遵循奈奎斯特準(zhǔn)則。這里,ADC的采樣時鐘由數(shù)字控制器提供,時鐘也充當(dāng)ODR。但是,由于需要有效地控制采樣保持時序才能獲得ADC的出色性能,因此該時鐘的時序靈活性較低,這也表明數(shù)字輸出時序需要盡可能與這些要求保持一致。

圖8.(a) DTSD ADC和(b) SAR ADC的時鐘要求。

了解這兩種架構(gòu)的時鐘要求后,可以看到ODR耦合到ADC的采樣時鐘,這在ODR可以動態(tài)漂移或改變或需要調(diào)諧為模擬輸入信號頻率的許多系統(tǒng)中都是一個限制因素。

CTSD ADC的優(yōu)勢:CTSD ADC可與新型異步采樣速率轉(zhuǎn)換器(ASRC)耦合,能夠以任何所需的ODR對核心ADC進(jìn)行重新采樣。ASRC還使設(shè)計人員能夠?qū)DR精確地設(shè)置為任意頻率,并突破了將ODR限制為采樣頻率倍數(shù)的舊限制。ODR的頻率和時序要求現(xiàn)在完全屬于數(shù)字接口的功能范圍,并且與ADC采樣頻率無關(guān)。該特性為信號鏈設(shè)計人員簡化了數(shù)字隔離設(shè)計。

第六步:與外部數(shù)字控制器接口

傳統(tǒng)上,ADC與數(shù)字控制器通信有兩種類型的數(shù)據(jù)接口模式。一種類型將ADC用作主機(jī),提供數(shù)字/ODR時鐘,并決定數(shù)字控制器的時鐘邊緣,以便輸入ADC數(shù)據(jù)。另一種類型為托管模式(接收器模式),其中數(shù)字控制器是主機(jī),提供ODR時鐘,并決定輸入ADC數(shù)據(jù)的時鐘邊緣。

從第5步開始,如果設(shè)計人員選擇DTSD ADC,該ADC將提供ODR時鐘,因此充當(dāng)后接的數(shù)字控制器的主機(jī)。如果選擇了SAR ADC,則數(shù)字控制器需要提供ODR時鐘,這意味著SAR ADC將始終配置為托管外設(shè)。因此,存在明顯的限制:一旦選擇ADC架構(gòu),數(shù)字接口就限制為主機(jī)模式或托管模式。目前,無論ADC架構(gòu)如何,都無法靈活地選擇接口。

CTSD ADC的優(yōu)勢:與CTSD ADC結(jié)合的新型ASRC使設(shè)計人員能夠獨(dú)立配置ADC數(shù)據(jù)接口模式。這為一些應(yīng)用開啟了全新的機(jī)會,在這些應(yīng)用中,無論ADC架構(gòu)如何,都可在適合數(shù)字控制器應(yīng)用的任何模式中配置高性能ADC。

將器件連接起來

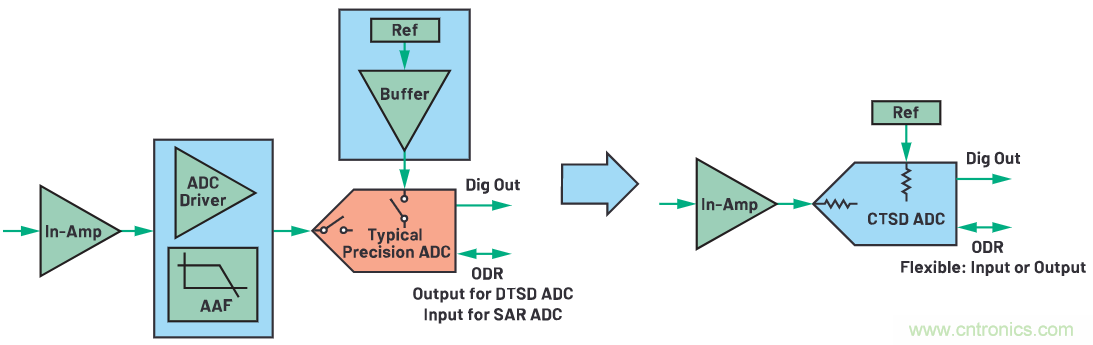

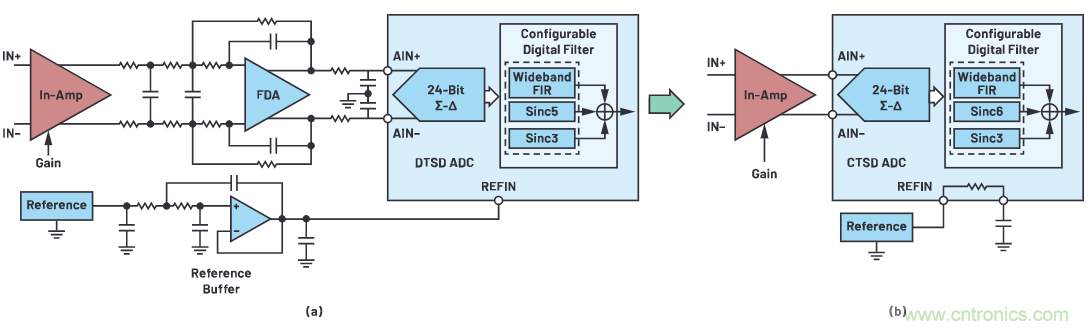

圖9顯示了傳統(tǒng)信號鏈的構(gòu)建模塊,其模擬前端(AFE)包含一個ADC輸入驅(qū)動器、一個混疊抑制濾波器和一個可通過CTSD ADC極大簡化的基準(zhǔn)電壓源緩沖區(qū)。圖10a顯示了一個采用DTSD ADC的示例信號鏈,該信號鏈需要大量的設(shè)計工作來微調(diào)和確定ADC的數(shù)據(jù)手冊性能。為了簡化客戶流程,ADI提供了 參考設(shè)計 ,可針對這些ADC的各種應(yīng)用重新使用或重新調(diào)整。

圖9.分別采用傳統(tǒng)精密ADC與CTSD ADC的信號鏈構(gòu)建模塊。

圖10b顯示了具有CTSD ADC及其簡化模擬輸入前端(AFE)的信號鏈,因?yàn)槠銩DC核心在輸入和基準(zhǔn)電壓源端沒有開關(guān)電容采樣器。開關(guān)采樣器移至ADC核心的后一級,使信號輸入和基準(zhǔn)電壓源輸入為純阻性。由此得出了幾乎無采樣混疊的ADC,使其自成其類。此外,這類ADC的信號轉(zhuǎn)換函數(shù)模擬抗混疊濾波器響應(yīng),這意味著它本身就能衰減噪聲干擾源。利用CTSD技術(shù),ADC可簡化為一個簡單的即插即用組件。

圖10.使用(a) DTSD技術(shù)與(b) CTSD技術(shù)的示例信號鏈。

總之,CTSD ADC簡化了信號鏈設(shè)計,同時實(shí)現(xiàn)了與傳統(tǒng)ADC信號鏈具有相同性能水平的系統(tǒng)解決方案,并具有以下優(yōu)勢:

● 提供了具有出色通道間相位匹配的無混疊、低延遲信號鏈

● 簡化了模擬前端,無需選擇并微調(diào)高帶寬輸入和基準(zhǔn)電壓源驅(qū)動緩沖區(qū)的額外步驟,可實(shí)現(xiàn)更高的通道密度

● 打破了ODR與采樣時鐘成函數(shù)關(guān)系的障礙

● 獨(dú)立控制與外部數(shù)字控制器的接口

● 提高了信號鏈可靠性評級,這是外設(shè)組件減少帶來的好處

● 減小了尺寸,BOM減少56%,為客戶縮短了產(chǎn)品上市時間

本系列的下一篇文章將探討CTSD ADC和ASRC如何幫助簡化信號鏈設(shè)計。本系列接下來的幾篇文章將更詳細(xì)地介紹CTSD ADC和ASRC的概念,重點(diǎn)說明信號鏈的優(yōu)勢,最后介紹如何利用新產(chǎn)品AD4134的特性。敬請持續(xù)關(guān)注,進(jìn)一步了解有助于簡化設(shè)計的突破性CTSD和ASRC技術(shù)的更多信息!

參考電路

“應(yīng)用筆記AN-282:采樣數(shù)據(jù)系統(tǒng)基本原理。” ADI公司。

驅(qū)動精密轉(zhuǎn)換器:選擇基準(zhǔn)電壓源和放大器。 ADI公司

Kester, Walt. “MT-021教程:ADC架構(gòu)II:逐次逼近型ADC。” ADI公司,2009年。

Σ-Δ ADC指南。ADI公司

Shaikh, Wasim and Srikanth Nittala. “輕松構(gòu)建交流和直流數(shù)據(jù)采集信號鏈。” 模擬對話,第54卷第3期,2020年8月。

致謝

作者感謝Naiqian Ren和Mark Murphy在撰寫本文時提供的有用見解。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進(jìn)行處理。

推薦閱讀: