【導(dǎo)讀】外置SRAM通常配有一個(gè)并行接口,考慮到大多數(shù)基于SRAM的應(yīng)用的存儲(chǔ)器要求�,選擇并行接口是必要的。對(duì)于已經(jīng)使用SRAM的高性能(主要是緩存)應(yīng)用而言��,與串行接口相比���,并行接口擁有明顯優(yōu)勢(shì)����。但這種情況似乎即將改變��。

盡管能夠提供高于串行接口的性能,但并行接口也有劣勢(shì)�����。其中最明顯的是��,無(wú)論是從電路板空間還是從引腳數(shù)要求的角度而言����,并行接口的尺寸都遠(yuǎn)遠(yuǎn)大于串行接口。例如���,一個(gè)簡(jiǎn)單的4Mb SRAM最多可能需要43個(gè)引腳才能與一個(gè)控制器相連���。在使用一個(gè)4Mb SRAM時(shí),我們的要求可能如下:

A.最多存儲(chǔ)256K的16位字

B.最多存儲(chǔ)512K的8位字

對(duì)于“A”����,我們需要使用18個(gè)引腳來(lái)選擇一個(gè)地址(因?yàn)榇嬖?^18種可能),并另需使用16個(gè)引腳來(lái)進(jìn)行實(shí)際上的數(shù)據(jù)輸入/輸出���。除了這34個(gè)引腳之外��,使能我們還需要更多連接來(lái)實(shí)現(xiàn)使能芯片����、使能使能輸出、使能使能寫入等功能�����。對(duì)于“B”����,我們需要的引腳相對(duì)較少:19個(gè)引腳用于選擇地址���,8個(gè)用于輸入/輸入��。但開(kāi)銷(使能芯片�、使能寫入等)保持不變����。對(duì)于一個(gè)容納這些引腳的封裝而言,僅從面積的角度而言���,其尺寸已經(jīng)很大��。

一旦地址被選擇后�,一個(gè)字(或其倍數(shù))將被快速讀取或?qū)懭搿?duì)于需要較高存取速度的應(yīng)用而言��,這些SRAM是理想選擇�。在使用SRAM的大多數(shù)常見(jiàn)系統(tǒng)中,這種優(yōu)勢(shì)使得“太多引腳”的劣勢(shì)變得可以忽略不計(jì)����,這些系統(tǒng)的控制器需要執(zhí)行極其復(fù)雜的功能,因此需要一個(gè)很大的緩存��。過(guò)去�,這些控制器通常較大,配有足夠的接口引腳��?�?刂破鬏^小��、引腳較少的應(yīng)用不得不湊合使用嵌入式RAM�����。

在一個(gè)配備串行接口的存儲(chǔ)器芯片中����,位元是被串行存取的(一次存取1位到4位)���。與并行接口相比,這使得串行接口更加簡(jiǎn)單和小巧�����,但通常吞吐量也更小�。這個(gè)劣勢(shì)讓大多數(shù)使用SRAM的系統(tǒng)棄用了串行接口。盡管如此�����,新一代應(yīng)用的存儲(chǔ)器要求有可能很快打破引腳數(shù)和速度之間的平衡����。

行業(yè)發(fā)展趨勢(shì)

處理器日趨強(qiáng)大��,尺寸越來(lái)越小�����。更加強(qiáng)大的處理器需要緩存進(jìn)行相應(yīng)的改進(jìn)��。但與此同時(shí),每一個(gè)新的工藝節(jié)點(diǎn)讓增加嵌入式緩存變得越來(lái)越困難���。SRAM擁有一個(gè)6晶體管架構(gòu)(邏輯區(qū)通常包含4個(gè)晶體管/單元)����。這意味著�,隨著工藝節(jié)點(diǎn)不斷縮小,每平方厘米上的晶體管的數(shù)量將會(huì)非常多���。這種極高的晶體管密度會(huì)造成很多問(wèn)題��,其中包括:

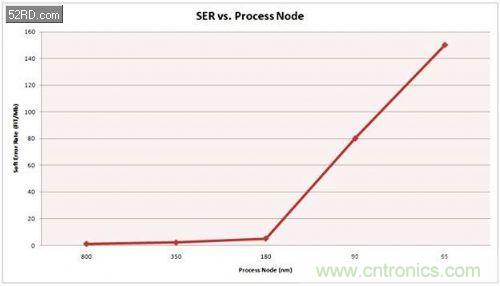

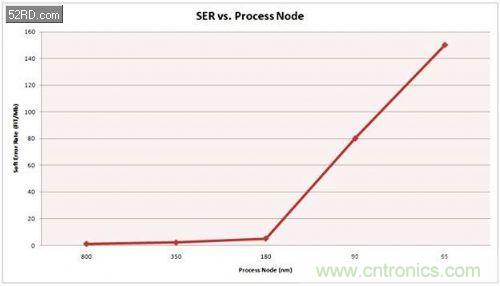

SER:軟錯(cuò)誤率�;Process node:工藝節(jié)點(diǎn) soft:軟錯(cuò)誤

更易出現(xiàn)軟錯(cuò)誤:工藝節(jié)點(diǎn)從130nm縮小到22nm后��,軟錯(cuò)誤率預(yù)計(jì)將增加7倍��。

更低的成品率:由于位單元隨著晶體管密度的增加而縮小��,SRAM區(qū)域更容易因工藝變化出現(xiàn)缺陷�����。這些缺陷將降低處理器芯片的總成品率�����。

更高的功耗:如果SRAM的位單元必需與邏輯位單元的大小相同,那么SRAM的晶體管就必須小于邏輯晶體管�。較小的晶體管會(huì)導(dǎo)致泄露電流升高,從而增加待機(jī)功耗�。

另一個(gè)技術(shù)發(fā)展趨勢(shì)是可穿戴電子產(chǎn)品的出現(xiàn)。對(duì)于智能手表�����、健身手環(huán)等可穿戴設(shè)備而言�,尺寸和功耗是關(guān)鍵因素。由于電路板的空間有限��,MCU必須做得很小����,而且必須能夠使用便攜式電池提供的微小電量運(yùn)行����。

片上緩存難以滿足上述要求。未來(lái)的可穿戴設(shè)備將會(huì)擁有更多功能����。因此�,片上緩存將無(wú)法滿足要求��,對(duì)外置緩存的需求將會(huì)升高����。在所有存儲(chǔ)器選項(xiàng)中,SRAM最適合被用作外置緩存�����,因?yàn)樗鼈兊拇龣C(jī)電流小于DRAM�,存取速度高于DRAM和閃存。

串行接口的崛起

當(dāng)我們觀察電子產(chǎn)品近些年的演進(jìn)歷程時(shí)�����,我們會(huì)注意到一個(gè)重要趨勢(shì):每一代設(shè)備的尺寸越來(lái)越小�,而性能卻保持不變甚至升高。這種縮小現(xiàn)象可以歸因于以下事實(shí):電路板上的每個(gè)組件都在變小��,從而造成了這樣的總體效果����。早在1965年,高登·摩爾就在他著名的摩爾定律中預(yù)測(cè)了電路的縮小趨勢(shì)�。但是����,這個(gè)縮小趨勢(shì)并未發(fā)生在所有類型的電路中�����。例如���,邏輯電路比SRAM電路縮小了很多倍�����。這造成了一個(gè)棘手的問(wèn)題:即嵌入式SRAM開(kāi)始占據(jù)90%的控制器空間�����。嵌入式SRAM的有限縮小還阻止了控制器以相應(yīng)于邏輯區(qū)域的程度縮小���。因此���,成本(與晶粒面積成正比)的降幅并未達(dá)到應(yīng)有的程度��。由于處理器/控制器的核心功能由邏輯區(qū)執(zhí)行���,將嵌入式SRAM移出芯片并以外置SRAM取而代之開(kāi)始具有意義�。

此外�����,可穿戴和物聯(lián)網(wǎng)設(shè)備的迅猛發(fā)展也是這一趨勢(shì)的推動(dòng)因素��。與其它任何設(shè)計(jì)要求相比��,這些設(shè)備最注重小巧的設(shè)計(jì)���。因此���,最小的MCU適合此類電路板,鑒于上述原因�,這個(gè)“最小的MCU”極有可能不搭載一個(gè)嵌入式緩存。同樣��,它也可能沒(méi)有太多的引腳��。

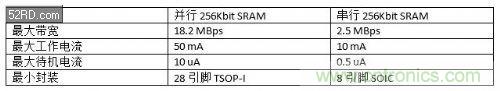

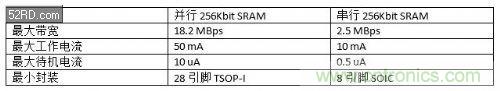

所有這些發(fā)展趨勢(shì)都指向一個(gè)要求:一個(gè)小巧����、能夠只扮演緩存的角色�、并能使用最小數(shù)量的引腳相連的外置SRAM����。串行SRAM就是專為滿足這個(gè)要求而量身定做的。存儲(chǔ)器在高速性能并非最重要因素的其它存儲(chǔ)器(DRAM�����、閃存等)中�����,串行接口已經(jīng)取代了并行接口��。由于存在需要SRAM的應(yīng)用���,串行SRAM在SRAM市場(chǎng)中一直處于小眾地位�����。在空間非常有限的特定應(yīng)用中��,它們一直是低功耗���、小尺寸替代方案����。目前,在峰值時(shí)鐘速率為20MHz(10MB/s帶寬)條件下��,串行SRAM最大容量為1Mbit。相比之下����,并行SRAM的帶寬高達(dá)250MB/s�,并支持最大64Mbit的容量��。下表對(duì)比了一個(gè)通用型256Kbit并行SRAM和一個(gè)256Kbit串行SRAM。

由于所需驅(qū)動(dòng)的引腳數(shù)較少����,而且速度更低����,串行接口存儲(chǔ)器通常比并行接口存儲(chǔ)器消耗更少的電能����,而且其最大的好處在于較小的尺寸-無(wú)論是從設(shè)備尺寸還是從引腳數(shù)的角度而言��。最小的并行 SRAM封裝是24球BGA����,而串行SRAM提供8引腳SOIC封裝。但必需注意的是��,WL-CSP是最小封裝���,很多并行和串行存儲(chǔ)器廠商支持CSP封裝�����。市場(chǎng)上的并行SRAM勝過(guò)串行SRAM的地方是性能-尤其是在存取時(shí)間上���。憑借寬得多的總線����,并行SRAM能夠最大支持200MBps的吞吐量��,而大多數(shù)得到廣泛使用的串行SRAM最多只支持40MBps。

如上表所示�����,存儲(chǔ)器存儲(chǔ)器串行接口存儲(chǔ)器在性能方面落后并行接口存儲(chǔ)器���。由于數(shù)據(jù)流是順序的�����,它們不能提供相同的吞吐量����。因此,串行存儲(chǔ)器存儲(chǔ)器最適合那些注重尺寸和功耗勝過(guò)存取時(shí)間的便攜式設(shè)備��,如手持設(shè)備和可穿戴設(shè)備。

未來(lái)將會(huì)怎樣

在物聯(lián)網(wǎng)和可穿戴設(shè)備興盛之前�����,串行 SRAM 的利潤(rùn)還不足以吸引主流SRAM廠商的注意力。實(shí)際上�����,主要的串行SRAM廠商就是Microchip和On-semi��。對(duì)于這兩家公司而言�,SRAM并非它們的核心業(yè)務(wù)����,在營(yíng)收中的占比也很小����。另一方面,靜態(tài)RAM領(lǐng)域的市場(chǎng)領(lǐng)袖(如賽普拉斯��、ISSI和Renesas)一直以來(lái)只專注于并行SRAM��。

這種情況可能會(huì)發(fā)生改變�。隨著串行SRAM的商機(jī)不斷增多,我們很快就會(huì)看到傳統(tǒng)的SRAM廠商將進(jìn)軍串行SRAM領(lǐng)域�����。未來(lái)幾年�����,串行SRAM的產(chǎn)品路線圖注定會(huì)出現(xiàn)(因?yàn)檫@些公司擁有積極推動(dòng)SRAM技術(shù)不斷進(jìn)步的悠久歷史)�����。容量和帶寬將是兩大推動(dòng)力��。靜態(tài)RAM領(lǐng)域的市場(chǎng)領(lǐng)袖賽普拉斯已經(jīng)將串行SRAM納入到其異步SRAM產(chǎn)品路線圖中���。事實(shí)上���,賽普拉斯和Spansion的合并意味著,賽普拉斯已經(jīng)掌握了最新的Hyperbus技術(shù)(由Spansion首創(chuàng))����,該技術(shù)能夠通過(guò)一個(gè)串行接口提供高達(dá)400MBps的吞吐量,因此���,在這方面完勝DRAM�。隨著主流SRAM廠商進(jìn)入該市場(chǎng)��,開(kāi)發(fā)人員不久將會(huì)獲得最先進(jìn)的串行SRAM�。

大吞吐量、小巧的串行接口SRAM給我們帶來(lái)了無(wú)限的可能性��。它最終有可能成為眾多電路板上當(dāng)代嵌入式SRAM和并行SRAM的全財(cái)產(chǎn)繼承者��。