【導讀】多路選擇器是數(shù)據(jù)選擇器的別稱。在多路數(shù)據(jù)傳送過程中,能夠根據(jù)需要將其中任意一路選出來的電路,叫做數(shù)據(jù)選擇器,也稱多路選擇器或多路開關。

什么是多路選擇器

多路選擇器是數(shù)據(jù)選擇器的別稱。在多路數(shù)據(jù)傳送過程中,能夠根據(jù)需要將其中任意一路選出來的電路,叫做數(shù)據(jù)選擇器,也稱多路選擇器或多路開關。

FPGA中多路選擇器結構

典型的FPGA器件主要包含3類基本資源:可編程邏輯塊(configurablelogicblock,CLB)、布線資源和可編程輸入/輸出模塊??删幊踢壿媺K四周被預制的布線資源通道包圍,可編程輸入/輸出模塊分布在FPGA四周,除了上述3種資源以外,通常在FPGA中還包含塊RAM、乘法器等可選資源。

在FPGA各種資源中,可編程邏輯塊是實現(xiàn)用戶功能的基本單元,每個可編程邏輯塊包含1個互連開關矩陣和4個SLICEs,其中每個SLICE包括2個查找表(Look-Up-Table,LUT)、2個觸發(fā)器和一些多路選擇器?;ミB開關矩陣主要由不同長度導線和多個布線開關組成,典型的布線開關結構如圖1所示。

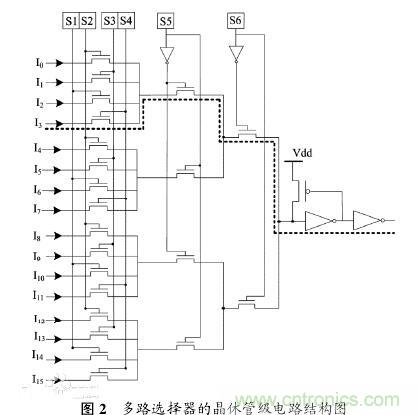

由圖1可見:每個布線開關由多路選擇器、緩沖器和一些可編程的SRAM單元構成。其中多路選擇器是連接各布線軌道和可編程邏輯塊的橋梁,其結構對FPGA的性能和功耗都有較大的影響。根據(jù)多路選擇器所驅動的導線長度不同,F(xiàn)PGA中多路選擇器的規(guī)模從4選1到30選1不等。圖2所示為16選1的多路選擇器晶體管級電路結構。

多路選擇器的左邊是 16 條輸入線,用于連接布線軌道或可編程邏輯塊等資源,S1~S6 代表 6 個可編程SRAM 單元,通過配置 SRAM 單元的內(nèi)容可以從 16條輸入線中選出 1 條作為有效輸入端,例如,當 S1~S6存儲單元的存儲值為“000100”時,輸入線 I3被選擇中,信號所經(jīng)過的有效路徑如圖 2 中虛線所示。多路選擇器的主體部分是傳輸晶體管,由于 NMOS 晶體管載流子的遷移效率高,電路速度快,因此,多路選擇器中的傳輸晶體管均采用 NMOS 晶體管實現(xiàn)。

多路選擇器工作原理

常用的多路選擇器有4選1、8選1、16選1等多種類型。下面以4選1數(shù)據(jù)選擇器為例介紹數(shù)據(jù)選擇器的工作原理。根據(jù)前面介紹的數(shù)據(jù)選擇器的功能,可以列出4選1數(shù)據(jù)選擇器的邏輯功能表,如表5-7-1所示。其中D0~D3為數(shù)據(jù)輸入端,A0、A1為數(shù)據(jù)選擇端。

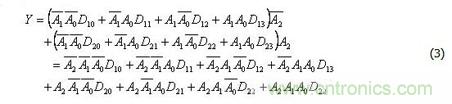

由邏輯功能表可以寫出輸出與輸入之間的表達式為

由邏輯表達式畫出4選1數(shù)據(jù)選擇器邏輯電路2所示。

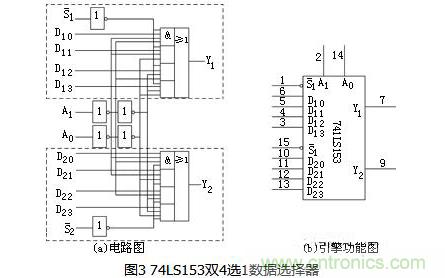

74LS153是一種集成的雙4選1數(shù)據(jù)選擇器邏輯器件。圖3所示為74LS153的邏輯電路圖和框圖。

由圖3(a)可知,74LS153的邏輯電路中包含兩個4選1數(shù)據(jù)選擇器,它們的數(shù)據(jù)輸入端分別為D10、D11、D12、D13和D20、D21、D22、D23,數(shù)據(jù)輸出端分別為Y1和Y2。它們有公共的地址選擇輸入端A0、A1。除此之外,還各自有有一個使能控制端

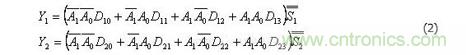

由圖3(a)可以寫出輸入與輸出之間的邏輯函數(shù)式為

由式(2)可以看出,只有當使能控制端

時,數(shù)據(jù)選擇器才能正常工作,否則數(shù)據(jù)輸出端鎖定在低電平。故使能控制端為低電平有效。

74LS153的邏輯功能表如表2所示。

表2 74LS153的邏輯功能表

多路選擇器的應用

(1)多路選擇器的擴展應用

可以用多片少數(shù)據(jù)輸入的數(shù)據(jù)選擇器設計多數(shù)據(jù)輸入的多路選擇器。

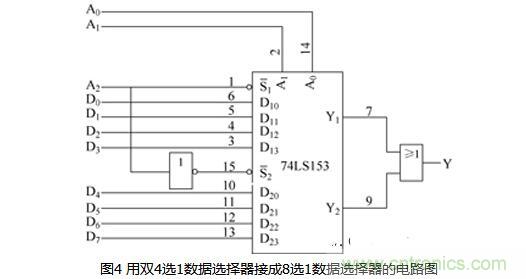

例1:用74LS153設計一個8選1的數(shù)據(jù)選擇器。

解:74LS153是一個雙4選1多路選擇器。有兩個公用的地址選擇輸入端,8個數(shù)據(jù)輸入端。8選1數(shù)據(jù)選擇器需要3個地址輸入端(23=8),因此需要用使能控制端來補充地址輸入端的不足。用雙4選1數(shù)據(jù)選擇器芯片74LS153設計的8選1數(shù)據(jù)選擇器的電路如圖4所示。

當A2=0時,上邊的4選1數(shù)據(jù)選擇器工作,根據(jù)地址輸入端A0、A1的狀態(tài),輸出端Y1選擇輸出D0~D3,此時Y2=0,故Y=Y1;當A2=1時,下邊的4選1數(shù)據(jù)選擇器工作,根據(jù)地址輸入端A0、A1的狀態(tài),輸出端Y2選擇輸出D4~D7,此時Y1=0,故Y=Y2。邏輯函數(shù)式為

也可以添加使能控制端對所接成的8選1數(shù)據(jù)選擇器的工作狀態(tài)進行控制。添加使能控制端的8選1數(shù)據(jù)選擇器的電路如圖5所示。

由圖5可知,當=0時,8選1數(shù)據(jù)選擇器正常工作;當=1時,8選1數(shù)據(jù)選擇器的輸出被鎖定在低電平。

(2)用多路選擇器設計組合邏輯電路

由表2可知,具有兩位地址輸入A0、A1的4選1數(shù)據(jù)選擇器,當使能控制端=0時,輸出與輸入之間的邏輯關系式為

若將A0、A1作為兩個輸入變量,同時令D0~D3為第三個變量的適當狀態(tài)(包括原變量、反變量、0和1),就可以用4選1數(shù)據(jù)選擇器實現(xiàn)任何形式的三變量組合邏輯函數(shù)。

同理,用由n位地址輸入端的多路選擇器可以實現(xiàn)任何形式的變量數(shù)不大于n+1的組合邏輯函數(shù)。

例2:用4選1數(shù)據(jù)選擇器實現(xiàn)以下組合邏輯函數(shù):

解:將式(4)化成與式(5)相對應的形式:

將式(6)與式(4)比較可知,只要令數(shù)據(jù)選擇器的數(shù)據(jù)輸入端為

則多路選擇器的輸出就是所要表達的組合邏輯函數(shù)。

多路選擇器的設計實現(xiàn)

設計一個二位4路選擇器,由于選擇器使用條件觸發(fā)的方法對應真值表進行匹配輸出與輸入,因此可以聯(lián)想到在C程序設計中的條件語句“If”和“Case”兩種,那么這兩種設計從硬件的角度出發(fā)有什么不同呢?

代碼如下:

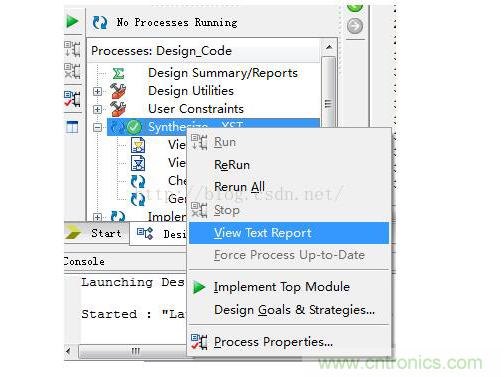

為了區(qū)別兩種設計的不同,可以查看ISE提供的綜合報告,操作如下:

綜合報告對比:

使用Case條件語句 使用IF條件語句

由綜合報告查看可知,if語句運用的元器件多于case語句運用的元器件,同時,if語句中每一個分支之間具有優(yōu)先級(串行),得到類似級聯(lián)的結構;而case語句所有分支處于同一優(yōu)先級(并行),綜合可以得到一個多路選擇器。因此,對于設計多路選擇器而言,if語句所造成的延時往往比case語句的大,所以對于多路選擇器而言,運用case語句的效果會更好。

Case語句下可能出現(xiàn)鎖存器。注釋case條件下的case語句塊的某一行可以得到不完整的case語句下的2位四路選擇器。由不完整case語句下的2位四路選擇器可知:由于case語句所有分支處于同一優(yōu)先級,所以當條件不完整時,對于處理結果,它不取決于語句的先后順序,只取決于待處理信號,而處理結果為與待處理信號相差1’b1的信號的處理結果,在這一條件下相當于與待處理信號相差1’b1的信號的處理結果得到了鎖存,鎖存器因此產(chǎn)生。

對與鎖存器而言,鎖存器在待處理信號存在Glitch的情況下,可能會對Glitch產(chǎn)生鎖存,從而導致鎖存出現(xiàn)嚴重錯誤,是目標信號處理結果與預期目的產(chǎn)生極大的偏差,因此鎖存器存在不穩(wěn)定因素,所以在使用鎖存器時,要牢記優(yōu)先消除待處理信號的Glitch。

測試文件:

initial begin

// Initialize Inputs

d0 = 0;

d1 = 1;

d2 = 2;

d3 = 3;

select = 0;

#100;

select = 1;

#100;

select = 2;

#100;

select = 3;

#100;

// Add stimulus here

end

仿真結果:

推薦閱讀: