【導(dǎo)讀】目前,電源在電子行業(yè)已經(jīng)占據(jù)舉足輕重的地位。數(shù)字電路設(shè)計(jì)師過去只是在PCB上留給電源設(shè)計(jì)人員一點(diǎn)空間(如果足夠大的話),并要求提供12V電壓?,F(xiàn)在電源的威力可大多了,不但可以讓電動(dòng)車跑得更遠(yuǎn),而且讓手機(jī)充電更快,甚至可以讓電力設(shè)備經(jīng)理節(jié)省兩位數(shù)的能源成本。

電源革命

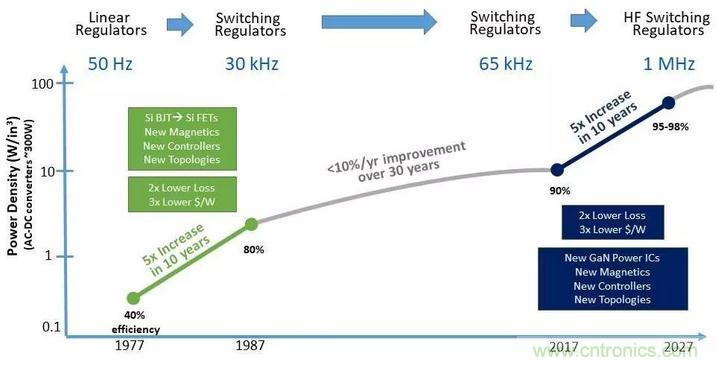

1977年HEXFET問世,它是由國際整流器公司(IR)的Alex Lidow和Dan Kenza領(lǐng)導(dǎo)的團(tuán)隊(duì)開發(fā)的。 Silicon General和Unitrod也在那一年開發(fā)出了電源管理芯片(PWMIC)。磁性材料也取得了突破,讓元器件變得更快。曾經(jīng)只在大學(xué)里出現(xiàn)的新型結(jié)構(gòu)突然變成了行業(yè)主流。讓開關(guān)電源成功商業(yè)化的核心技術(shù)發(fā)生在20世紀(jì)70年代后期。

功率半導(dǎo)體、拓?fù)?、控制器和磁性材料的大融合為業(yè)界帶來了驚人的變化:效率提高、相應(yīng)功率密度增加,同時(shí)成本直線下降。這為電子行業(yè)的大量開發(fā)鋪平了道路,為我們帶來了很多新的技術(shù),比如諧振電源、LLC轉(zhuǎn)換器,以及英飛凌突破性的CoolMOS技術(shù)。

寬禁帶半導(dǎo)體代表了功率電子的第二次革命。這些新型功率半導(dǎo)體激發(fā)了控制器公司的新控制器和改進(jìn)的拓?fù)浣Y(jié)構(gòu),如90年代后期推出的有源鉗位反激式技術(shù)。此外,最新的磁性元件可在一兆赫茲或兩兆赫茲下工作。同樣,在這場革命中,效率提高、頻率上升,成本卻不斷下降。

圖1:電源發(fā)展歷程

功率密度(AC-DC轉(zhuǎn)換器~300W);線性調(diào)節(jié)器;開關(guān)調(diào)節(jié)器;高頻開關(guān)調(diào)節(jié)器;新磁性元件;新控制器;新拓?fù)浣Y(jié)構(gòu);2倍低損耗;3倍低成本/W;10年5倍提升;超過30年每年<10%改善;十年5倍提升;新GaN功率IC;效率。

運(yùn)行更快

過去幾年來,磁性能方面取得了重大進(jìn)展,而且出現(xiàn)了改進(jìn)的材料。就拿GaN來說,兩年前人們還認(rèn)為磁性不存在,為什么還要試圖加快速度呢,但現(xiàn)在已經(jīng)證明事實(shí)并非如此。

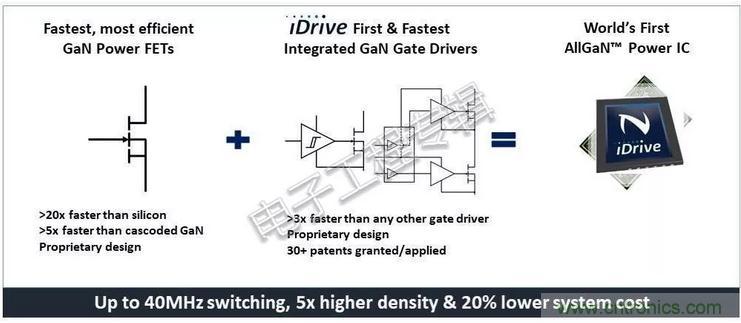

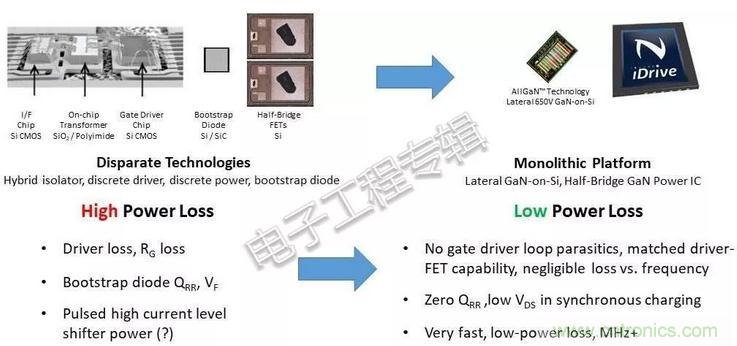

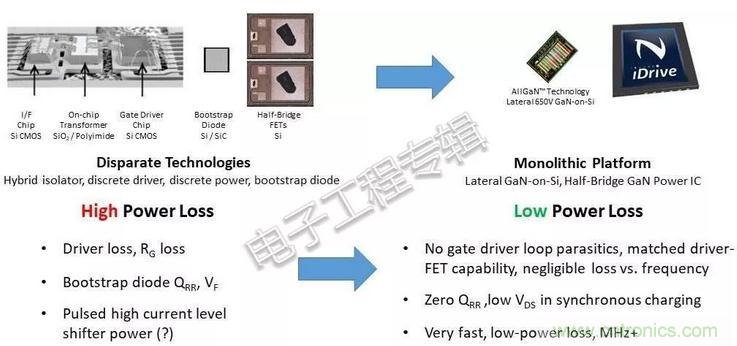

隨著半導(dǎo)體和磁性技術(shù)的快速發(fā)展,控制器也是一個(gè)需要開發(fā)的領(lǐng)域,要跟上其他相關(guān)器件的快速發(fā)展。以Navitas公司的AllGaN技術(shù)為例,該公司采用增強(qiáng)模式GaN FET,并將之與驅(qū)動(dòng)器集成在同一芯片上。 Navitas還可以集成其他器件,如電平轉(zhuǎn)換器或ECD二極管,甚至是邏輯欠壓鎖定,使其更接近真正的GaN功率芯片。

圖2:AllGaN功率芯片的特性

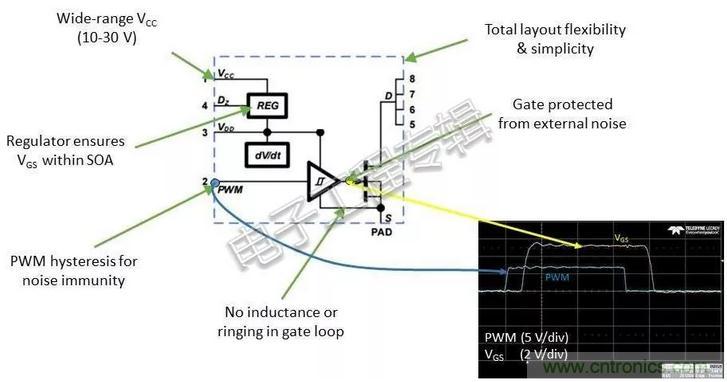

由于這一切都發(fā)生在單個(gè)芯片上,因此相對(duì)容易制造和封裝,這自然也帶來了其他系統(tǒng)好處。由于FET的柵極直接連接到柵極驅(qū)動(dòng)器的輸出,因此驅(qū)動(dòng)器輸出和柵極輸入之間的阻抗為零。 這也意味著GaN作為分立器件不容易搞定,但如果你能在一個(gè)盒子里集成一個(gè)完整的解決方案,那就意味著你可以小心地控制流向柵極的電壓,這意味著也可以保護(hù)柵極。

集成的方案還意味著可以在高頻工作,而不必?fù)?dān)心柵極阻抗會(huì)影響性能、效率和穩(wěn)定性。 另一個(gè)優(yōu)點(diǎn)是集成的驅(qū)動(dòng)器可以提高穩(wěn)健性,使用單芯片解決方案,布局也比較靈活。

圖3:GaN芯片集成解決方案

寬范圍Vcc;調(diào)節(jié)器可保護(hù)SOA內(nèi)的VGS;滯后的PWM可抗噪聲干擾;整體布局靈活簡潔;柵極可防止外部噪聲。

開關(guān)

在高頻應(yīng)用中,軟開關(guān)諧振拓?fù)涫且环N很好的方法。 但在實(shí)際情況下,可能存在啟動(dòng)例程,也許是突發(fā)模式,你可以進(jìn)行硬切換。 要知道一切都非常艱難,可以可靠地進(jìn)行硬切換,也可以進(jìn)行軟切換。

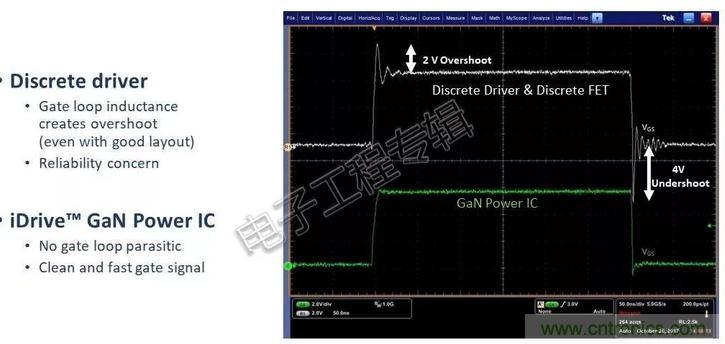

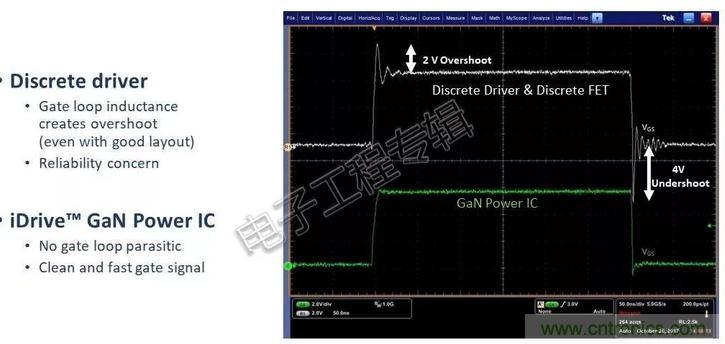

沒有柵極阻抗或電阻的分立解決方案會(huì)產(chǎn)生不穩(wěn)定的電路。 如果添加了阻抗,它會(huì)變得穩(wěn)定,但也會(huì)導(dǎo)致很長的開關(guān)周期。 因此,如果可以直接連接驅(qū)動(dòng)器輸出和柵極輸入,那么就可以快速運(yùn)行并保持穩(wěn)定。壓擺率只需要一個(gè)電阻即可搞定。 因此,集成意味著一種非??煽氐母咝阅芷骷?/div>

圖4:分離驅(qū)動(dòng)器和分離FET與GaN功率芯片性能比較

關(guān)于集成的另一個(gè)問題是ESD。標(biāo)準(zhǔn)硅MOSFET的ESD非常容易理解。PWMIC的ESD也是眾所周知的。而GaN器件是分立形式的,其ESD就不是那么容易理解。我們必須要小心,但如果你要設(shè)計(jì)功率IC,那么就要將ESD二極管放在上面。因此,這也成為通過集成使生活變得更為輕松的另一種方式,可以集成電平移位器,或半橋直通保護(hù)之類的東西。

在這種情況下,集成解決方案占板面積為6×8mm,具有完整的半橋系統(tǒng)和自舉充電功能,以及欠壓鎖定和ESD保護(hù)特性。在頻率方面,這些器件的額定值為2兆赫茲。關(guān)于高頻電平轉(zhuǎn)換的一個(gè)注意事項(xiàng)是,存在電感耦合或電容耦合的技術(shù)可以進(jìn)行電平轉(zhuǎn)換,但其本質(zhì)上是不同的技術(shù)。

集成的優(yōu)勢(shì)

在易用性方面,相對(duì)于分立方案,帶驅(qū)動(dòng)器的集成方案可明顯減少組件數(shù)量,使設(shè)計(jì)更具可預(yù)測(cè)性,而且設(shè)計(jì)速度也更快,性能更高。集成是控制和性能的關(guān)鍵。集成的解決方案可提供一個(gè)可預(yù)測(cè)的構(gòu)建模塊。

圖5:分離方案與集成方案的對(duì)比

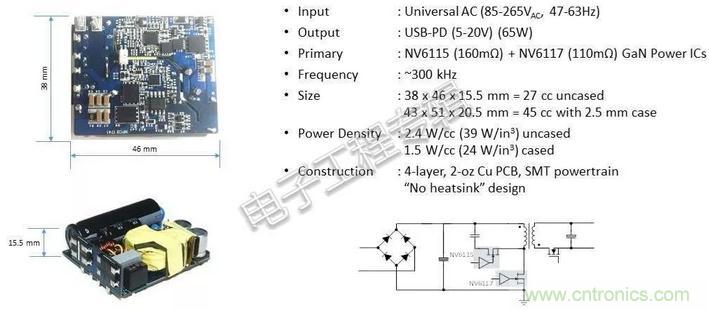

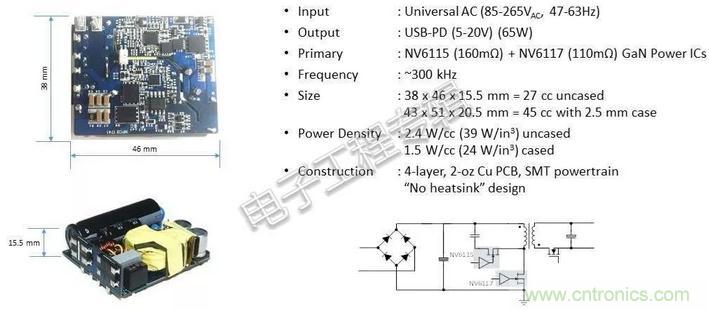

圖6示出了一個(gè)65W電源參考設(shè)計(jì)的示例,這是一種采用軟開關(guān)型態(tài)、運(yùn)行頻率約為300kHz的有源鉗位反激式設(shè)計(jì)。 對(duì)于標(biāo)準(zhǔn)反激式或準(zhǔn)諧振反激式設(shè)計(jì),緩沖網(wǎng)絡(luò)處理反激電壓。 用第二個(gè)開關(guān)替換緩沖網(wǎng)絡(luò),它就變成了一個(gè)半橋,能夠?qū)㈩l率提高到300kHz。

圖6:一個(gè)65W電源參考設(shè)計(jì)示例

有源鉗位由弗吉尼亞理工大學(xué)(Virginia Polytech)于1996年推出,現(xiàn)在的控制IC不僅可以達(dá)到很高的功率密度,而且還滿足DoE六級(jí)要求和歐盟要求。 該設(shè)計(jì)是具有完整USB-PD輸出的最小電源,比標(biāo)準(zhǔn)電源具有更高的復(fù)雜性和功能,在90V AC輸入的最壞情況下可以提供20V輸出,其滿負(fù)載效率超過93%。

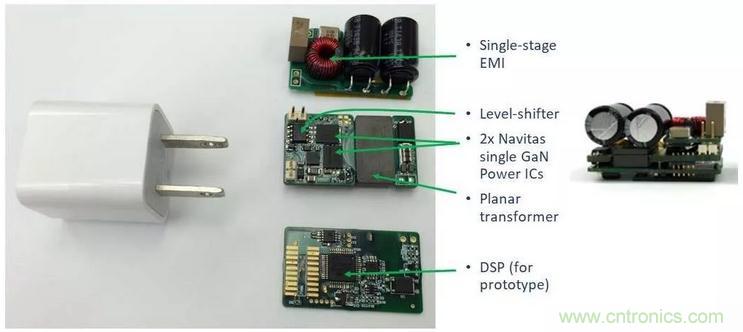

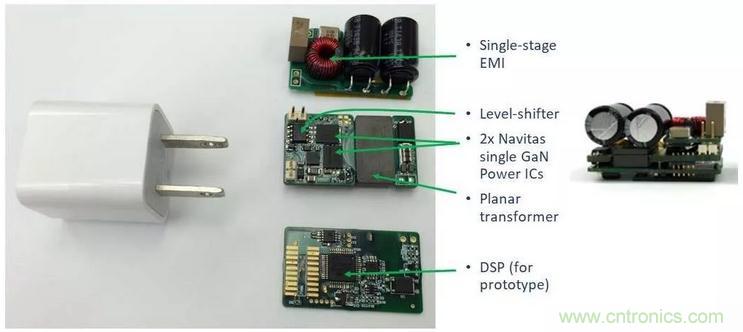

圖7顯示了使用相同拓?fù)涞恼缀赵O(shè)計(jì)。這實(shí)際上是由弗吉尼亞理工大學(xué)CPES研究小組于2016年完成的。這個(gè)一兆赫的有源鉗位反激設(shè)計(jì)使用DSP而不是控制IC,以證明滿載的頻率和功率密度。但在過去,它不可能成為一個(gè)行業(yè)產(chǎn)品,因?yàn)樗谳p載情況下效率不高。 現(xiàn)在使用控制IC就可以做到這一點(diǎn)。

圖7:與65W電源相同拓?fù)浣Y(jié)構(gòu)的兆赫茲電源

在高頻率時(shí)要考慮的事情之一就是EMI,可能有一個(gè)大約500kHz的臨界點(diǎn),你可以使用一個(gè)基于線軸的變壓器,或一個(gè)基于環(huán)形的變壓器。如果在500kHz左右使用平面變壓器,需要注意一些事情。其一是可以得到尺寸非常小的設(shè)計(jì),這有助于提高功率密度。其二是可以獲得相同或更低成本的變壓器解決方案,因?yàn)槟悴槐亟?jīng)歷制作整個(gè)繞線變壓器的額外步驟。

你可以在任何一方進(jìn)行PCB設(shè)計(jì)。但在這種設(shè)計(jì)中,在平面變壓器內(nèi)部,還有一些EMI屏蔽層,因此它可以阻止EMI,或者從源頭消除EMI。所以在這種情況下,我們可以得到一個(gè)非常非常小的單面EMI濾波器,它符合所有規(guī)格。

由于這是一個(gè)使用DSP的大學(xué)項(xiàng)目,利用新的控制器和新的半橋,我們可以再次縮小這個(gè)設(shè)計(jì)的尺寸。

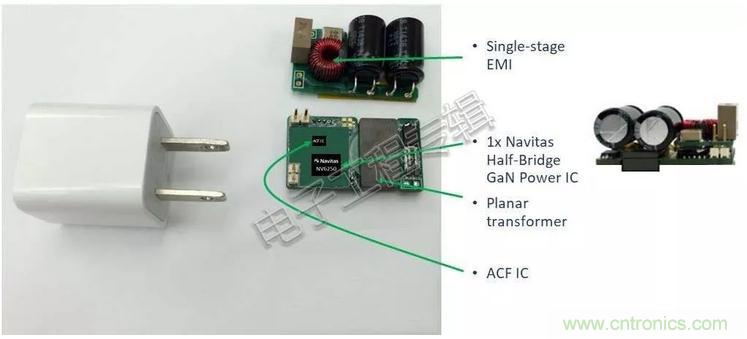

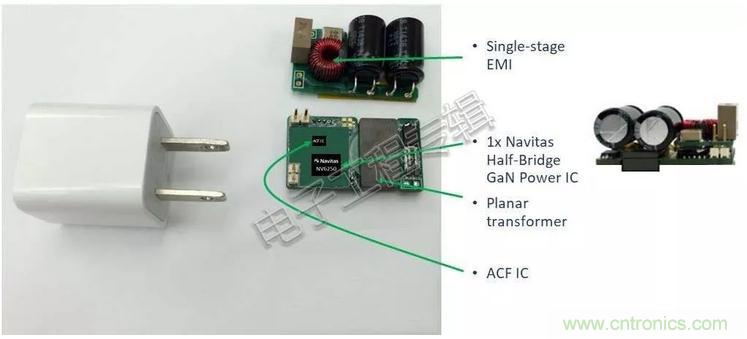

圖8:縮小后的兆赫茲電源

現(xiàn)在,在與標(biāo)準(zhǔn)的5W或7W方糖電源相同的空間內(nèi),我們可以做到25W。這是使用的是GaN,新的磁性材料,這是日立的ML 91S器件。使用新的拓?fù)鋵W(xué),以前只是在學(xué)術(shù)界,現(xiàn)在已經(jīng)在企業(yè)界流行起來,以及可用的控制IC,再集成驅(qū)動(dòng)器和MOSSFET,可以充分利用所有這些來推動(dòng)性能的進(jìn)一步提升。