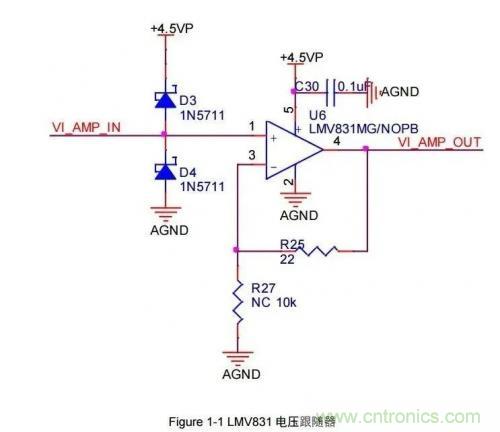

【導(dǎo)讀】跟隨器電路:前級采樣電阻上的采樣電壓 VI_AMP_IN 經(jīng) U6 的跟隨作用 VI_AMP_OUT 送至 ADC 進(jìn)行 A/D 轉(zhuǎn)換,U6 在此處的作用:減輕“負(fù)載效應(yīng)”提高采集精度。

跟隨器電路:

前級采樣電阻上的采樣電壓 VI_AMP_IN 經(jīng) U6 的跟隨作用 VI_AMP_OUT 送至 ADC 進(jìn)行 A/D 轉(zhuǎn)換,U6 在此處的作用:減輕“負(fù)載效應(yīng)”提高采集精度。D3,D4 為運放的輸入保護(hù)二極管,當(dāng)輸入異常電壓比電源電壓還要高 VF(二極管正向?qū)▔航担┗蛘弑鹊仉娢坏?VF 時,二極管將會導(dǎo)通鉗位。

1 LMV831 的主要特性

其一,該運放輸入誤差電壓 VOS 最大為 1mV,有利于提高整體精度;

其二,由于采用 CMOS 工藝,輸入偏置電流低至 0.1pA,故不需要在消除偏置電壓上花費額外精力;

其三,輸出驅(qū)動電流達(dá)到 30mA,很適合與 ADC 配合使用;

其四,該運放在 1.8GHz 的頻率下 EMIRR 高達(dá) 120dB,這一特性有利于抵抗板上射頻模塊的干擾;

其五,軌至軌輸出,在單電源供電條件下非常重要。

2 輸出特性

從上表可以看出負(fù)載越重,運放輸出軌至軌特性越差,但因為本次案例運放后級是連接低速 ADC,因此負(fù)載很輕,取表中的 6mV(VOH)和 5mV(VOL)作為典型值即可。

單電源供電條件下,會將負(fù)載電阻 RL 接至 V+/2,實則是以 V+/2 作為虛擬地。

3 仿真驗證

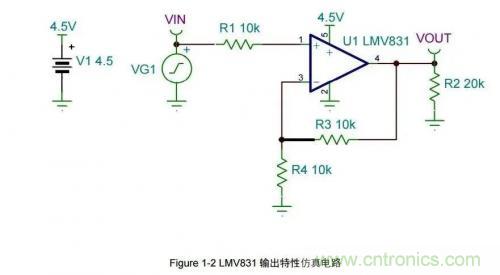

建立仿真電路如下:

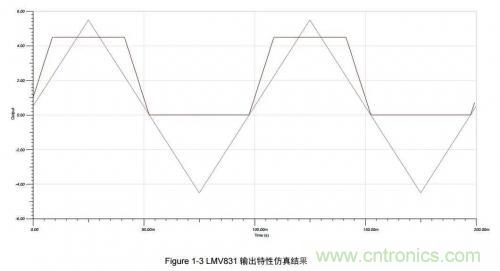

如 Figure 1-2 所示,將 LMV831 搭成放大倍數(shù)為 2 的同相放大器,同時輸入幅值為 5V,頻率為 10Hz 的三角波(為了能讓輸出飽和),仿真結(jié)果如 Figure 1-3 所示,顯然,輸出幅度非常接近 LMV831 的供電電壓 4.5V,量得幅值為 4.49V(梯形波形的平臺部分),波形下端也接近 0V,從而證實了該運放的軌至軌輸出特性。

4 軌到軌,還有細(xì)節(jié)需要注意

ADC 的可接受電壓范圍為 0~4.096V,而現(xiàn)在 LMV831 搭成的跟隨器可以支持 0~4.49V 的輸出,似乎萬事俱備,若前級采樣電壓也是 0~4.096V 范圍(即運放輸入電壓),整個電路堪稱完美!然而,直覺告訴我,事情肯定沒這么簡單。我突然想起當(dāng)初選型時,TI 的運放篩選條件下,有一個 Rail-to-Rail 選項:

這個選項從左到右分別為:輸入軌至軌,輸出軌至軌,輸入到正軌,輸入到負(fù)軌——等等,那么 LMV831 是否支持軌至軌輸入?我滿懷期待,然而遺憾的是,LMV831 數(shù)據(jù)手冊并未提及輸入是否也是軌至軌,進(jìn)一步查閱發(fā)現(xiàn)該運放在 3.3V 供電時,共模輸入范圍為 -0.1V~2.1V!也就是說 3.3V 供電的時候,LMV831 是不支持軌至軌輸入的!

5 輸入特性

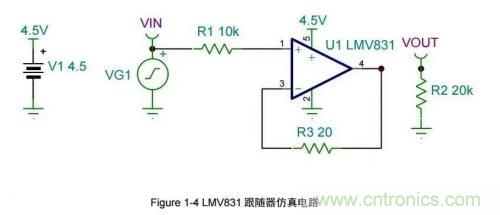

運放的共模輸入范圍與供電電壓密切有關(guān),電壓越高,輸入范圍越大。為了驗證 4.5V 供電電壓下的最高不失真輸入電壓,搭建了 Figure 1-4 所示的仿真電路。

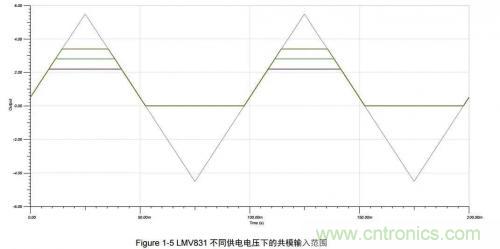

對該電路執(zhí)行“參數(shù)仿真”,分別測試供電電壓為 3.3V、3.9V、4.5V 下的輸出電壓,如 Figure 1-5 所示,三角波為輸入波形,3 個類似等腰梯形的波形為運放輸出,其中,暗黃色為 4.5V 供電電壓時的輸出,綠色對應(yīng) 3.9V 供電電壓,紫色對應(yīng) 3.3V 供電電壓,顯而易見:第一,LMV831 并非軌至軌輸入;第二,該運放的共模輸入范圍隨供電電壓的提高而擴(kuò)大,在 4.5V 供電電壓下跟隨器(增益為 1)最大輸出電壓約為 3.39V,也即最大輸入電壓為 3.39V。簡言之,4.5V 供電電壓下,LMV831 的最大共模輸入電壓(不失真)為 3.39V。

在得知這個真相之后,一方面將運放的供電電壓從 3.3V 提高到 4.5V,提高輸出的范圍,另一方面將采樣電阻值改小,從而讓最大采樣電壓小于 3.39V,從而規(guī)避了改板的風(fēng)險!

6 實際驗證

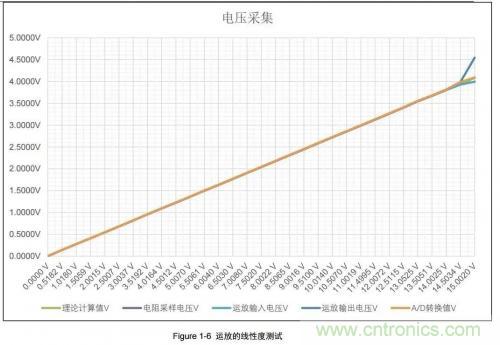

實際產(chǎn)品中用了 91:34 的電阻對輸入 0~10V 進(jìn)行分壓,分壓再經(jīng)電壓跟隨器送至 ADC 進(jìn)行 A/D 轉(zhuǎn)換,分別測量電阻采樣電壓、運放輸入端電壓、運放輸出端電壓、A/D 轉(zhuǎn)換電壓,繪出 Figure 1-6。

留意表格 1-2 的數(shù)據(jù),隨著運放輸入電壓緩慢接近“閾值”,傳遞誤差急劇增加,當(dāng)輸入電壓為 3.9954V 時,運放索性飽和輸出 4.5460V!通過繪制圖表 Figure 1-6 可以很明顯觀察到這個現(xiàn)象,從而證實了猜想。實際上我的目的也達(dá)到了,因為我只需要 0~12V 外部輸入時線性度滿足 0.2% F.S 就足夠了。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進(jìn)行處理。