[導讀]在PCB設計中,由于采用了瞬態(tài)電壓抑止器(TVS)二極管來抑止因ESD放電產生的直接電荷注入,因此PCB設計中更重要的是克服放電電流產生的電磁干擾(EMI)電磁場效應。本文介紹了一些常用的PCB設計中的ESD抑制準則。

PCB布線是ESD防護的一個關鍵要素,合理的PCB設計可以減少故障檢查及返工所帶來的不必要成本。在PCB設計中,由于采用了瞬態(tài)電壓抑止器(TVS)二極管來抑止因ESD放電產生的直接電荷注入,因此PCB設計中更重要的是克服放電電流產生的電磁干擾(EMI)電磁場效應。本文將提供可以優(yōu)化ESD防護的PCB設計準則。

電路環(huán)路的設計

電流通過感應進入到電路環(huán)路,這些環(huán)路是封閉的,并具有變化的磁通量。電流的幅度與環(huán)的面積成正比。較大的環(huán)路包含有較多的磁通量,因而在電路中感應出較強的電流。因此,必須減少環(huán)路面積。

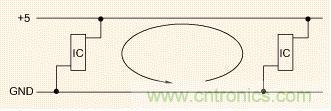

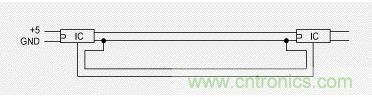

圖1,常見的電路環(huán)路

最常見的環(huán)路如圖1所示,由電源和地線所形成。在可能的條件下,可以采用具有電源及接地層的多層PCB設計。多層電路板不僅將電源和接地間的回路面積減到最小,而且也減小了ESD脈沖產生的高頻EMI電磁場。

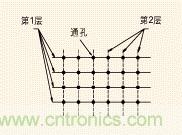

圖2,電源線和接地線的網格狀連接

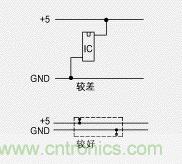

如果不能采用多層電路板,那么用于電源線和接地的線必須連接成如圖2所示的網格狀。網格連接可以起到電源和接地層的作用,用過孔連接各層的印制線,在每個方向上過孔連接間隔應該在6厘米內。另外,在布線時,將電源和接地印制線盡可能靠近也可以降低環(huán)路面積,如圖3所示。

圖3,布線時將電源和接地印制線盡可能靠近也可以降低環(huán)路面積

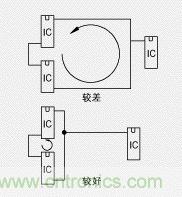

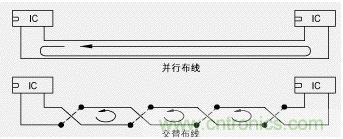

減少環(huán)路面積及感應電流的另一個方法是減小互連器件間的平行通路,見圖4。

圖4,減小互連器件間的平行通路

長信號線的處理

長的信號線也可成為接收ESD脈沖能量的天線,盡量使用較短信號線可以降低信號線作為接收ESD電磁場天線的效率。盡量將互連的器件放在相鄰位置,以減少互連的印制線長度。

當必須采用長于30厘米的信號連接線時,可以采用保護線,如圖5所示。一個更好的辦法是在信號線附近放置地層。信號線應該距保護線或接地線層13毫米以內。

圖5,長于30厘米信號連接線可以采用保護線

如圖6所示,將每個敏感元件的長信號線(>30厘米)或電源線與其接地線進行交叉布置。交叉的連線必須從上到下或從左到右的規(guī)則間隔布置。

圖6,敏感元件的長信號線或電源線與其接地線交叉布置

地電荷注入

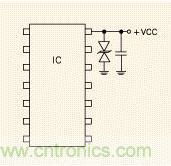

ESD對地線層的直接放電可能損壞敏感電路。在使用TVS二極管的同時還要使用一個或多個高頻旁路電容器,這些電容器放置在易損元件的電源和地之間。旁路電容減少了電荷注入,保持了電源與接地端口的電壓差。

TVS使感應電流分流,保持TVS鉗位電壓的電位差。TVS及電容器應放在距被保護的IC盡可能近的位置(見圖7),要確保TVS到地通路以及電容器管腳長度為最短,以減少寄生電感效應。

圖7,TVS及電容器應放在距被保護的IC盡可能近的位置

連接器必須安裝到PCB上的銅鉑層。理想情況下,銅鉑層必須與PCB的接地層隔離,通過短線與焊盤連接。

保護電路中的寄生電感

TVS二極管通路中的寄生電感在發(fā)生ESD事件時會產生嚴重的電壓過沖。盡管使用了TVS二極管,由于在電感負載兩端的感應電壓VL=L×di/dt,過高的過沖電壓仍然可能超過被保護IC的損壞電壓閾值。

保護電路承受的總電壓是TVS二極管鉗位電壓與寄生電感產生的電壓之和,VT=VC+VL。一個ESD瞬態(tài)感應電流在小于1ns的時間內就能達到峰值(依據IEC 61000-4-2標準),假定引線電感為每英寸20nH,線長為四分之一英寸,過沖電壓將是50V/10A的脈沖。經驗設計準則是將分流通路設計得盡可能短,以此減少寄生電感效應。

所有的電感性通路必須考慮采用接地回路,TVS與被保護信號線之間的通路,以及連接器到TVS器件的通路。被保護的信號線應該直接連接到接地面,若無接地面,則接地回路的連線應盡可能短。TVS二極管的接地和被保護電路的接地點之間的距離應盡可能短,以減少接地平面的寄生電感。

最后,TVS器件應該盡可能靠近連接器以減少進入附近線路的瞬態(tài)耦合。雖然沒有到達連接器的直接通路,但這種二次輻射效應也會導致電路板其它部分的工作紊亂。

PCB設計的其它準則

1.避免在PCB邊緣安排重要的信號線,如時鐘和復位信號等;

2.將PCB上未使用的部分設置為接地面;

3.機殼地線與信號線間隔至少為4毫米;

4.保持機殼地線的長寬比小于5:1,以減少電感效應;

5.用TVS二極管來保護所有的外部連接;