【導(dǎo)讀】在設(shè)計高速電路板時,自動化設(shè)計工具有時不能發(fā)現(xiàn)一些不很明顯但卻非常重要的問題。比如:工藝過程的變化是怎樣引起實際阻抗發(fā)生變化的?這里只要在設(shè)計的早期步驟當中采取一些措施就可以避免這種問題。

本文闡述了工藝過程的變化是怎樣引起實際阻抗發(fā)生變化的,以及怎樣用精確的現(xiàn)場解決工具(field solver)來預(yù)見這種現(xiàn)象。即使沒有工藝的變化,其它因素也會引起實際阻抗很大的不同。在設(shè)計高速電路板時,自動化設(shè)計工具有時不能發(fā)現(xiàn)這種不很明顯但卻非常重要的問題。然而,只要在設(shè)計的早期步驟當中采取一些措施就可以避免這種問題。這種技術(shù)稱做“防衛(wèi)設(shè)計”(defensive design)。

疊層數(shù)問題

一個好的疊層結(jié)構(gòu)是對大多數(shù)信號整體性問題和EMC問題的最好防范措施,同時也最易被人們誤解。這里有幾種因素在起作用,能解決一個問題的好方法 可能會導(dǎo)致其它問題的惡化。很多系統(tǒng)設(shè)計供應(yīng)商會建議電路板中至少應(yīng)該有一個連續(xù)平面以控制特性阻抗和信號質(zhì)量,只要成本能承受得起,這是個很好的建議。EMC咨詢專家時常建議在外層上放置地線填充(ground fill)或地線層來控制電磁輻射和對電磁干擾的靈敏度,在一定條件下這也是一種好建議。

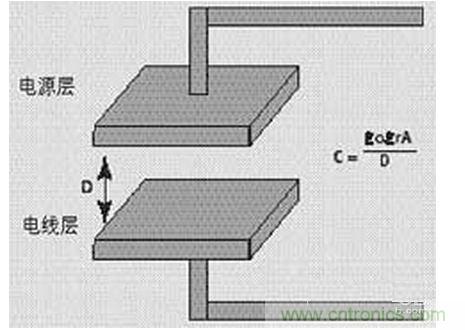

圖1:用電容模型分析疊層結(jié)構(gòu)中的信號問題

然而,由于瞬態(tài)電流的原因,在某些普通設(shè)計中采用這種方法可能會遇到麻煩。 首先,我們來看一對電源層/地線層這種簡單的情況:它可看作為一個電容??梢哉J為電源層和地線層是電容的兩個極板。要想得到較大的電容值,就需將兩個極板靠得更近(距離D),并增大介電常數(shù)(ε▼r▼)。電容越大則阻抗越低,這是我們所希望的,因為這樣可以抑制噪聲。不管其它層怎樣安排,主電源層和地線層應(yīng)相鄰,并處于疊層的中部。如果電源層和地線層間距較大, 就會造成很大的電流環(huán)并帶來很大的噪聲。如果對一個8層板,將電源層放在一側(cè)而將地線層放在另一側(cè),

將會導(dǎo)致如下問題:

1. 最大的串擾。由于交互電容增大,各信號層之間的串擾比各層本身的串擾還大。

2. 最大的環(huán)流。電流圍繞各電源層流動且與信號并行,大量電流進入主電源層并通過地線層返回。EMC特性會由于環(huán)流的增大而惡化。

3. 失去對阻抗的控制。信號離控制層越遠,由于周圍有其它導(dǎo)體因此阻抗控制的精度就越低。

4. 由于容易造成焊錫短路,可能會增加產(chǎn)品的成本。

我們必須在性能和成本之間進行折衷選擇,因此,怎樣安排數(shù)字電路板以獲得最好的SI和EMC特性呢?

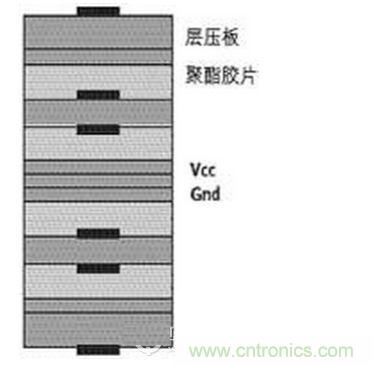

PCB的各層分布一般是對稱的。不應(yīng)將多于兩個的信號層相鄰放置;否則,很大程度上將失去對SI的控制。最好將內(nèi)部信號層成對地對稱放置。除非有些信號需要連線到SMT器件,我們應(yīng)盡量減少外層的信號布線。

圖2:優(yōu)秀設(shè)計方案的第一步是正確設(shè)計疊層結(jié)構(gòu)

對層數(shù)較多的電路板,我們可將這種放置方法重復(fù)很多次。也可以增加額外的電源層和地線層;只要保證在兩個電源層之間沒有成對的信號層即可。

高速信號的布線應(yīng)安排在同一對信號層內(nèi);除非遇到因SMT器件的連接而不得不違反這一原則。一種信號的所有走線都應(yīng)有共同的返回路徑(即地線層)。有兩種思路和方法來判斷什么樣的兩個層能看成一對:

1. 保證在相等距離的位置返回信號完全相等。這就是說,應(yīng)將信號對稱地布線在內(nèi)部地線層的兩側(cè)。這樣做的優(yōu)點是容易控制阻抗和環(huán)流;缺點是地線層上有很多過孔,而且有一些無用的層。

2. 相鄰布線的兩個信號層。優(yōu)點是地線層中的過孔可控制到最少(用埋式過孔);缺點是對某些關(guān)鍵信號這種方法的有效性下降。

采用第二種方法的話,元件驅(qū)動和接收信號的接地連接最好能夠直接連接到與信號布線層相鄰的層面。作為一個簡單的布線原則,表層布線寬度按英寸計應(yīng)小于按毫微妙計的驅(qū)動器上升時間的三分之一(例如:高速TTL 的布線寬度為1英寸)。

如果是多電源供電,在各個電源金屬線之間必須鋪設(shè)地線層使它們隔開。不能形成電容,以免導(dǎo)致電源之間的AC耦合。

上述措施都是為了減少環(huán)流和串擾,并增強阻抗控制能力。地線層還會形成一個有效的EMC“屏蔽盒”。在考慮對特性阻抗的影響的前提下,不用的表層區(qū)域都可以做成地線層。

[page]

特性阻抗

一種好的疊層結(jié)構(gòu)就能夠作到對阻抗的有效控制,其走線可形成易懂和可預(yù)測的傳輸線結(jié)構(gòu)?,F(xiàn)場解決工具能很好地處理這類問題,只要將變量數(shù)目控制到最少,就可以得到相當精確的結(jié)果。

但是,當三個以上的信號層疊在一起時,情況就不一定是這樣了,其理由很微妙。目標阻抗值取決于器件的工藝技術(shù)。高速CMOS 技術(shù)一般能達到約70Ω; 高速TTL器件一般能達到約80Ω至100Ω。因為阻抗值通常對噪聲容限和信號切換有很大的影響,所以進行阻抗選擇時需要非常仔細;產(chǎn)品說明書對此應(yīng)當給出指導(dǎo)。

現(xiàn)場解決工具的初始結(jié)果可能會遇到兩種問題。首先是視野受到限制的問題,現(xiàn)場解決工具只對附近走線的影響做分析,而不考慮影響阻抗的其它層上的非平行走線。現(xiàn)場解決工具在布線前,即分配走線寬度時無法知道細節(jié),但上述成對安排的方法可使這個問題變得最小。

值得一提的是不完全電源層(partial power planes)的影響。外層電路板上在布線后經(jīng)常擠滿了接地銅線,這樣就有利于抑制EMI和平衡涂敷(balance plating)。如果只對外層采取這樣的措施,則本文所推薦的疊層結(jié)構(gòu)對特性阻抗的影響非常微小。

大量采用相鄰信號層的效果是非常顯著的。某些現(xiàn)場解決工具不能發(fā)現(xiàn)銅箔的存在,因為它只能檢查印制線和整個層面,所以對阻抗的分析結(jié)果是不正確的。當鄰近的層上有金屬時,它就象一個不太可靠的地線層一樣。如果阻抗過低,瞬時電流就會很大,這是一個實際而且敏感的EMI問題。

導(dǎo)致阻抗分析工具失敗的另一個原因是分布式電容。這些分析工具一般不能反映引腳和過孔的影響(這種影響通常用仿真器來進行分析)。這種影響可能會很大,特別是在背板上。其原因非常簡單:特性阻抗通??捎孟率龉接嬎悖?/div>

√L/C

其中,L和C分別是單位長度的電感和電容。

如果引腳是均勻排布的,附加的電容將大大影響這個計算結(jié)果。公式將變成:

√L/(C+C'')

C''是單位長度的引腳電容。

如果象在背板上那樣連接器之間用直線相連,就可用總線路電容以及除了第一和最后一個引腳之外的總引腳電容。這樣,有效阻抗就就會降低,甚至可能從 80Ω降到8Ω。為了求得有效值,需將原阻抗值除以:

√(1+C''/C)

這種計算對于元件選擇是很重要的。

延遲

模擬時,應(yīng)該考慮元件和封裝的電容(有時還應(yīng)包括電感)。要注意兩個問題。首先,仿真器可能不能正確模擬分布式電容;其次,還要注意不同生產(chǎn)情況對不完全層面和非平行走線的影響。許多現(xiàn)場解決工具都不能分析沒有全電源或地線層的疊層分布。然而,如果與信號層相鄰的是一個地線層,那么計算出的延遲會相當糟糕,比如電容,會有最大的延遲;如果一個雙面板的兩層都布有許多地線和VCC 銅箔,這種情況就更嚴重。如果過程不是自動化的話,在一個CAD系統(tǒng)中設(shè)置這些東西將會是很繁亂的。

EMC

EMC的影響因素很多,其中許多因素通常都沒能得到分析,即使得到分析, 也往往是在設(shè)計完成以后,這就太遲了。下面是一些影響EMC的因素:

1. 電源層的槽縫會構(gòu)成了四分之一波長的天線。對于金屬容器上需開安裝槽的場合,應(yīng)采用鉆孔方法來代替。

2. 感性元件。我曾碰到過一位設(shè)計人員,他遵循了所有的設(shè)計規(guī)則,也作了仿真,但他的電路板仍然有很多輻射信號。原因是:在頂層有兩個電感相互平行放置,構(gòu)成了變壓器。

3. 由于不完全接地層的影響,內(nèi)層低阻抗引起外層較大的瞬態(tài)電流。

采用防衛(wèi)設(shè)計可以避免這些問題中的大多數(shù)。首先應(yīng)該作出正確的疊層結(jié)構(gòu)和布線方略,這樣就有了好的開始。

這里沒有涉及某些基本問題,比如網(wǎng)絡(luò)拓撲、信號失真原因和串擾計算方法;只是分析了一些敏感的問題,以幫助讀者應(yīng)用從EDA系統(tǒng)得到的結(jié)果。任何分析都要依賴于所采用的模型,分析不到的因素也會對結(jié)果產(chǎn)生影響。過于復(fù)雜就象太不精確一樣,避免過多參量的變化(如印制線寬度等),有助于整齊、一致的設(shè)計。