【導讀】對于今天的電子產(chǎn)品,我們應該通過在集成電路中設(shè)計堅固的ESD結(jié)構(gòu)來覆蓋所有ESD基板,但大多數(shù)情況下,工程師都默認器件是安全合規(guī)的,很少考慮ESD保護。

對于今天的電子產(chǎn)品,我們應該通過在集成電路中設(shè)計堅固的ESD結(jié)構(gòu)來覆蓋所有ESD基板,但大多數(shù)情況下,工程師都默認器件是安全合規(guī)的,很少考慮ESD保護。

ESD(Electro-Static discharge)的意思是“靜電釋放”。ESD是20世紀中期以來形成的以研究靜電的產(chǎn)生、危害及靜電防護等的學科。因此,國際上習慣將用于靜電防護的器材統(tǒng)稱為ESD,中文名稱為靜電阻抗器。

靜電放電或ESD的定義是在不同靜電電位下的靜電電荷在物體或表面之間的轉(zhuǎn)移。放電會在短時間內(nèi)釋放超高壓,在1至100納秒(ns)的千伏(kV)范圍內(nèi)??梢韵胂?,對于這些類型的電壓和時間單位,ESD事件具有快速邊沿。當發(fā)生這樣的事件時,靜電荷快速轉(zhuǎn)移會造成可見或不可見的火花。

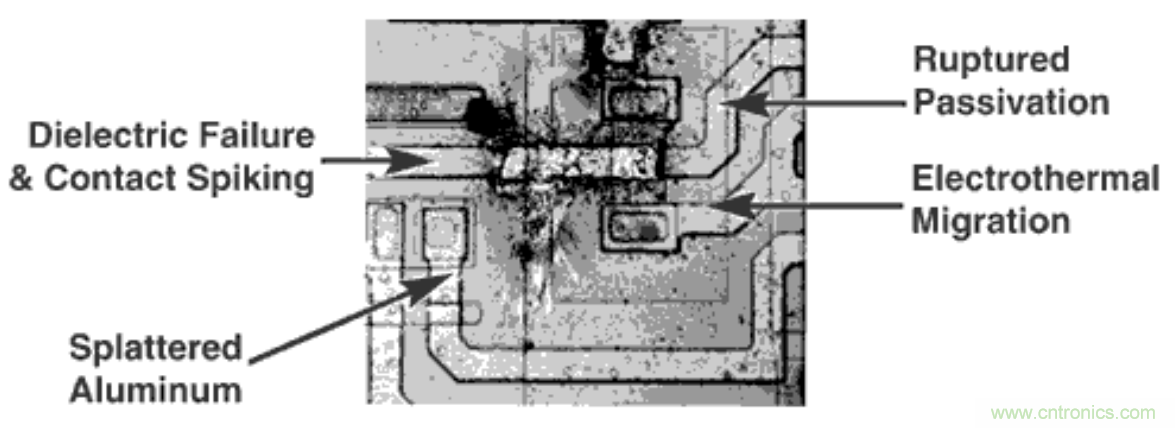

ESD通常只有敏感的電子設(shè)備才能檢測到,通過觸摸沒有ESD保護的設(shè)備,個人很可能在不知不覺中對器件造成破壞性的損壞。在高度充電的ESD環(huán)境中,其封裝內(nèi)的ESD保護硅芯片將被破壞(如圖1)。

圖1.芯片ESD損壞的放大示例,顯示金屬跡線消失,鈍化破裂和一種熱遷移。 (:Maxim Integrated,應用筆記639)

在圖1中,芯片發(fā)生ESD事件,所造成的損害是災難性的,具有蒸發(fā)的金屬痕跡,受損的鈍化區(qū)域以及可能的電熱遷移軟錯誤。從技術(shù)上講,如果電路仍然可以工作,軟錯誤(例如規(guī)格降級)可能會在以后出現(xiàn)。

這種類型的損壞最容易在封裝過程中或在芯片組裝到PCB之前發(fā)生。IC的內(nèi)部ESD保護電路在預裝配處理和裝配操作期間為芯片提供了一些保護。在這種環(huán)境中,低阻抗接地路徑用作放電路徑。在封測環(huán)境中,低阻抗接地路徑的實現(xiàn)包括腕帶,接地地板,接地桌面和ESD電離器。一旦IC安裝在PCB中并與其他組件互連,這種受保護的環(huán)境就會大大降低。需要通過適當?shù)腅SD控制和預防,減少ESD損壞。

人們經(jīng)常在與周圍環(huán)境相互作用時產(chǎn)生靜電火花,這些靜電會破壞芯片原本的特性,此類事故每年都會造成數(shù)十億美元的損失。在選擇最終產(chǎn)品之前,請務(wù)必遵循實驗室中的良好ESD預防措施,并查看產(chǎn)品數(shù)據(jù)表中的ESD保護規(guī)范。