【導讀】本系列第一部分介紹了鎖相環(huán)(PLL),說明了其基本架構和工作原理。 另外舉例說明了PLL在通信系統(tǒng)中的用途。 在第二部分中,我們詳細考察了相位噪聲、參考雜散、輸出漏電流等關鍵性能規(guī)格,還考慮了它們對系統(tǒng)性能的影響。 在本部分中,我們將考察PLL頻率合成器的主要構建模塊。 我們還將比較整數(shù)N和小數(shù)N架構。 最后將總結市場上現(xiàn)有的VCO,同時列出ADI的現(xiàn)有頻率合成器系列。

PLL頻率合成器可以從多個基本構建模塊的角度來考察。 我們在前面已經(jīng)提到過這個問題,下面將更加詳細地進行探討:

鑒頻鑒相器(PFD)

參考計數(shù)器(R)

反饋計數(shù)器(N)

鑒頻鑒相器(PFD)

頻率合成器的核心是鑒相器,也稱鑒頻鑒相器。 在鑒相器中,將比較參考頻率信號與從VCO輸出端反饋回來的信號,結果得到的誤差信號用于驅動環(huán)路濾波器和VCO。 在數(shù)字PLL (DPLL)中,鑒相器或鑒頻鑒相器是一個邏輯元件。三種最常用的實現(xiàn)方法為:

異或(EXOR)柵極

J-K觸發(fā)器

數(shù)字鑒頻鑒相器

這里,我們只考慮PFD,這也是ADF4110和ADF4210頻率合成器系列中使用的元件,因為與EXOR柵極和J-K觸發(fā)器不同,處于解鎖狀態(tài)時,其輸出為頻差以及兩個輸入間相差的函數(shù)。

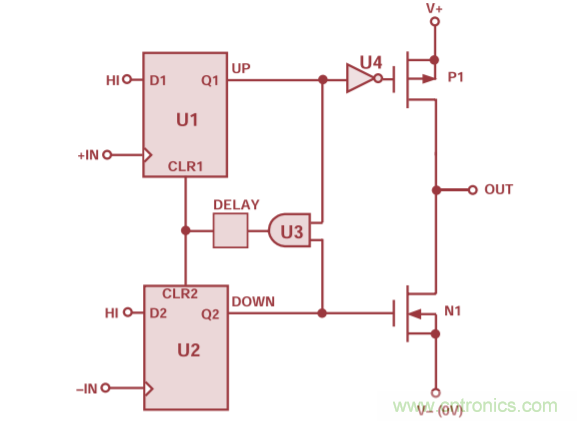

圖1所示為PFD的一種實現(xiàn)方案,該類器件基本上由兩個D型觸發(fā)器組成。 一路Q輸出使能正電流源,另一路Q輸出則使能負電流源。 假設本設計中D型觸發(fā)器由正邊沿觸發(fā),則狀態(tài)為(Q1, Q2):

11—兩個輸出均為高電平,由反饋至觸發(fā)器上CLR引腳的AND柵極(U3)禁用。

00—P1和N1均關閉,輸出OUT實際處于高阻抗狀態(tài)。

10—P1開啟,N1關閉,輸出位于V+。

01—P1關閉,N1開啟,輸出位于V–。

圖1. 運用D型觸發(fā)器的典型PFD。

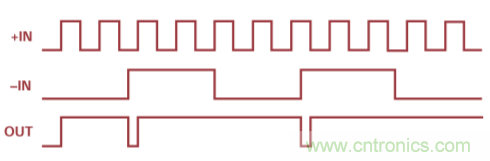

現(xiàn)在考慮系統(tǒng)失鎖且+IN處的頻率遠高于–IN處的頻率時電路的性能表現(xiàn),如圖2所示。

圖2. PFD波形(鎖頻和鎖相均解除)。

由于+IN處的頻率遠高于–IN處的頻率,因此輸出多數(shù)時間處于高電平狀態(tài)。 +IN上的第一個上升沿會發(fā)送輸出高電平,并且這種情況會一直持續(xù)到–IN上出現(xiàn)第一個上升沿。在實際的系統(tǒng)中,這就意味著輸出及VCO的輸入會被進一步拉高,進而造成–IN處的頻率增加。這恰恰是期望達到的效果。

如果+IN處的頻率遠低于–IN處的,則會出現(xiàn)相反效果。 OUT處的輸出多數(shù)時間處于低電平狀態(tài)。 這會在負方向上驅動VCO,并再次使得–IN處的頻率更加接近+IN處的頻率,從而達到鎖定條件。 圖3顯示了輸入處于鎖頻和接近鎖相條件時的波形。

圖3. PFD波形(鎖頻,但相位鎖定解除)。

由于+IN領先于–IN,因此輸出為一系列正電流脈沖。 這些脈沖往往會驅動VCO,使得–IN信號變得與+IN信號相位對齊。

發(fā)生這種情況時,如果U3和U1及U2的CLR輸入端之間沒有任何延遲元件,那么輸出可能會進入高阻抗模式,從而既不會生成正電流脈沖,也不會生成負電流脈沖。 這并不是一種很好的狀況。 VCO會發(fā)生漂移,直到造成顯著的相位誤差并再次開始生成正電流脈沖或負電流脈沖。 這種循環(huán)會持續(xù)相當長的一段時間,其影響是電荷泵的輸出會被某個信號(PFD輸入?yún)⒖碱l率的次諧波)調制。 由于這可能是一種低頻信號,因此無法通過環(huán)路濾波器進行衰減,從而會導致VCO輸出頻譜中出現(xiàn)非常明顯的雜散,該現(xiàn)象稱為“間隙”效應。 通過在U3的輸出端和U1及U2的CLR輸入端之間添加延遲元件,可以確保不會發(fā)生這種情況。 添加延遲元件后,即使+IN和–IN相位完全對齊時,電荷泵輸出端仍會生成電流脈沖。 該延遲的持續(xù)時間等于在U3輸出處插入的延遲,稱為反沖防回差脈沖寬度。

參考計數(shù)器

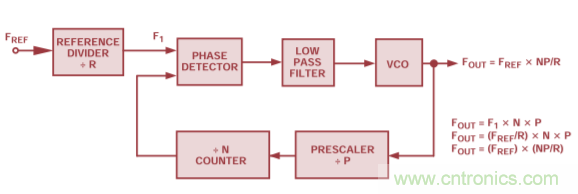

在傳統(tǒng)的整數(shù)N分頻頻率合成器中,輸出頻率的分辨率由施加于鑒相器的參考頻率決定。 因此,舉例來說,如果需要200 kHz間距(如GSM電話中),那么參考頻率必須為200 kHz。 但是,獲取穩(wěn)定的200 kHz頻率源并不容易。 一種合理的做法是采用基于晶振的良好高頻源并對其進行分頻。 例如,從10 MHz頻率基準開始并進行50分頻,就可以得到所需的頻率間隔。這種方法如圖4所示。

圖4 在PLL頻率合成器中使用參考計數(shù)器。

反饋計數(shù)器N

N計數(shù)器也稱為N分頻器,是用于設置PLL中輸入頻率和輸出頻率之間關系的可編程元件。 N計數(shù)器的復雜性逐年增長。 除簡單的N計數(shù)器之外,經(jīng)過發(fā)展,后來還包括“預分頻器”,后者可具有“雙模”。

這種結構已經(jīng)發(fā)展成為下列情況下固有問題的一種解決方案:需要超高頻輸出時使用基本N分頻結構來反饋至鑒相器。 例如,我們假設需要一個間距為10 Hz的900 MHz輸出。 可以使用10 MHz參考頻率并將R分頻器設為1000。然后,反饋中的N值必須為90,000。這意味著,至少需要一個能夠處理900 MHz輸入頻率的17位計數(shù)器。

為處理此范圍,需要考慮在可編程計數(shù)器之前加上一個固定計數(shù)器元件,以便將超高輸入頻率拉低至標準CMOS的工作頻率范圍內。 該計數(shù)器稱為預分頻器,如圖5所示。

然而,使用標準的預分頻器會導致其他并發(fā)癥。 現(xiàn)在,系統(tǒng)分辨率降低(F1 × P)。 可通過使用雙模預分頻器來解決這個問題(圖6)。 這種方法可以享有標準預分頻器種種優(yōu)勢,又不會犧牲系統(tǒng)分辨率。 雙模預分頻器是一種可通過外部控制信號將分頻比從一個值切換為另一個值的計數(shù)器, 通過使用帶有A和B計數(shù)器的雙模預分頻器,仍可以保持F1的輸出分辨率。 不過,必須滿足下列條件:

圖5. 基本預分頻器。

圖6. 雙模預分頻器。

1.如果兩個計數(shù)器未超時,其輸出信號都為高電平。

2.當B計數(shù)器超時時,其輸出變?yōu)榈碗娖?,并立即將兩個計數(shù)器加載至其預設值。

3.加載到B計數(shù)器的值必須始終大于加載到A計數(shù)器的值。

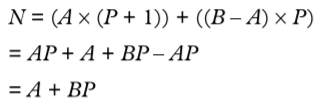

假設B計數(shù)器剛發(fā)生超時并且兩個計數(shù)器均已經(jīng)重新加載值A和B。我們來看看再次達到相同狀態(tài)所需的VCO周期數(shù)。

只要A計數(shù)器未超時,預分頻器即會以P + 1進行分頻。因此,每次預分頻器計數(shù)達到(P + 1)個VCO周期時,A和B計數(shù)器都會遞減1。 這意味著,A計數(shù)器會在((P + 1) × A)個VCO周期后超時。 然后,預分頻器會切換至P分頻。也可以說,此時B計數(shù)器還有(B – A)個周期才會超時。 所需時間為: ((B – A) × P)。 現(xiàn)在,系統(tǒng)會返回到剛開始的初始條件。

所需的VCO周期總數(shù)為:

在使用雙模預分頻器時,必須考慮N的最低值和最高值。這里,我們真正想要的是可以按離散整數(shù)步長更改N的范圍??紤]表達式N = A + BP。為確保N有連續(xù)的整數(shù)間距,A必須在0至(P – 1)之間。這樣,每當B遞增時,就有充足的分辨率來填充BP 和(B + 1)P之間的所有整數(shù)值。

就如我們針對雙模預分頻器提到的那樣,B必須大于或等于A,雙模預分頻器才能正常工作?;诖?,我們可以說,若要按離散整數(shù)步長遞增,最小分頻比為:

N 的最高值來自

本例中,Amax 和Bmax僅僅取決于A和B計數(shù)器的大小。接下來,我們將給出一個采用ADF4111的例子。

我們假設,通過編程將預分頻器的分頻比設為32/33。

A計數(shù)器: 6位意味著,A可能為26– 1 = 63

B計數(shù)器: 13位意味著,B可能為213 – 1 = 8191

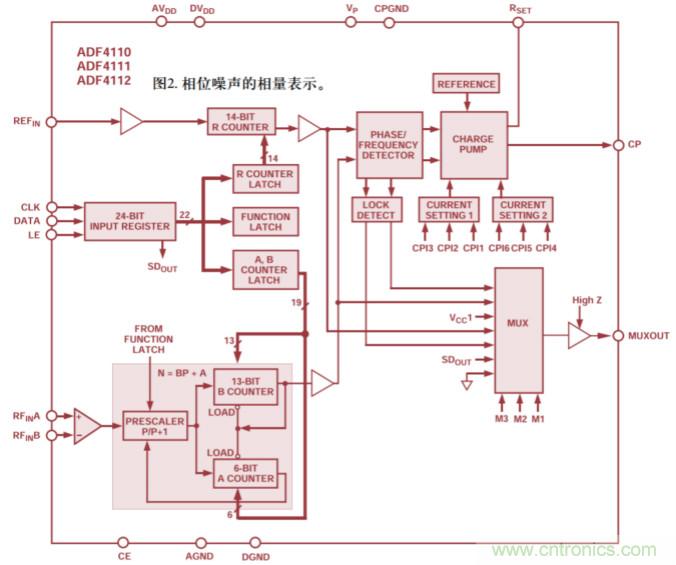

ADF4110系列

前面幾節(jié)討論的構建模塊在來自ADI公司的新型整數(shù)N頻率合成器系列中均有使用。ADF4110系列頻率合成器由單個器件構成,ADF4210系列由雙通道版本構成。ADF4110的框圖如下所示。其中含有上面描述的參考計數(shù)器、雙模預分頻器、N計數(shù)器和PFD模塊。

圖7. ADF4110系列的框圖。

小數(shù)N頻率合成器s*

許多新興無線通信系統(tǒng)都要求本振(LO)具有更快的切換能力和更低相位噪聲。整數(shù)N頻率合成器要求參考頻率等于通道間距。該值可能非常低,意味著高N。該高N會產(chǎn)生相應較高的相位噪聲。低參考頻率會限制PLL鎖定時間。小數(shù)N合成是在PLL中同時實現(xiàn)低相位噪聲和快速鎖定時間的一種方式。

這種技術最初出現(xiàn)在20世紀70年代初。早期工作主要由惠普公司和Racal公司完成。該技術最初稱為“digiphase”,但后來被廣泛稱為小數(shù)N。

在標準頻率合成器中,只能用一個整數(shù)除以RF信號。這就需要使用一個相對較低的參考頻率(取決于系統(tǒng)通道間距),并在反饋中導致高N值。這兩個事實都對系統(tǒng)建立時間和系統(tǒng)相位噪聲有著重要影響。低參考頻率意味著較長的建立時間,高N值意味著較大的相位噪聲。

如果反饋中可能出現(xiàn)除數(shù)為小數(shù)的情況,則可以使用較高的參考頻率,同時實現(xiàn)通道間距目標。小數(shù)越小,則意味著相位噪聲越低。

事實上,通過交替除以兩個整數(shù),可以實現(xiàn)在較長時間內用小數(shù)除(通過先后除以2和3可以除以2.5)。

那么,如何除以X或(X + 1)(假設小數(shù)在這兩個值之間)? 數(shù)值的小數(shù)部分可以按參考頻率速率累加。

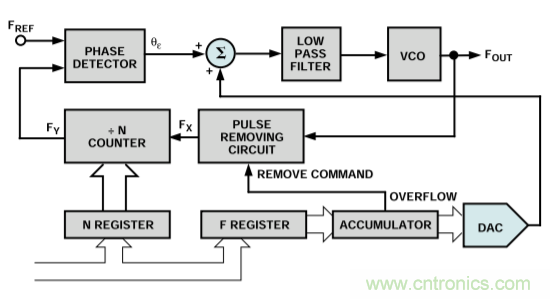

圖8. 小數(shù)N頻率合成器。

然后,每當累加器溢出時,就可以用該信號來更改N分頻比。在圖8中,這是通過移除饋入N計數(shù)器的一個脈沖來實現(xiàn)的。實際上,每當累加器溢出時,結果會使分頻比加1。另外,F(xiàn)寄存器中的數(shù)值越大,累加器溢出次數(shù)越多,以較大數(shù)值為除數(shù)的次數(shù)也就越多。這正是電路的目的所在。但會增加一些并發(fā)癥。從N分頻電路饋入鑒相器的信號在實時表現(xiàn)上并不均勻。相反,其調制速率取決于參考頻率和編程小數(shù)。結果又調制鑒相器輸出,并進入VCO輸入端。最后,在VCO輸出端會出現(xiàn)較多的雜散內容。目前業(yè)界正在努力解決這些雜散問題。 一種方法是采用DAC,如圖8所示。

目前為止,單芯片小數(shù)N頻率合成器仍然未能達到預期,但最終可以實現(xiàn)的效益意味著,其發(fā)展正在快馬加鞭地進行。

VCO制造商小結

在過去5年中,隨著無線通信的爆炸式增長,對頻率合成器、VCO等產(chǎn)品的需求也出現(xiàn)了大幅增長。 有意思的是,到目前為止,為市場提供服務的制造商分為涇渭分明的兩個陣營。 以下列出了VCO領域的部分制造商。 列表并未窮盡所有制造商,只是讓讀者獲得對一些主要參與者的認識。

VCO

ADI頻率合成器系列

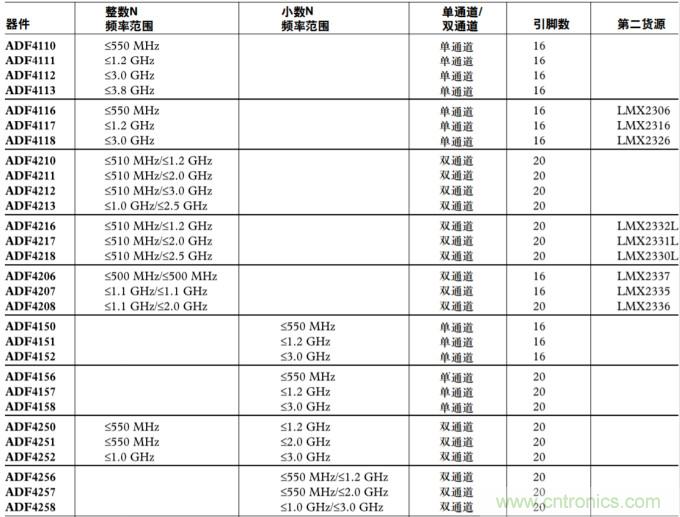

下表列出了ADF4xxx頻率合成器系列的未來成員, 其中包括單通道和雙通道器件,以及整數(shù)N和小數(shù)N器件。

致謝

ADF4xxx系列頻率合成器在愛爾蘭利默里克的ADI工廠中設計。 產(chǎn)品線團隊包括: Mike Tuthill、Leo McHugh、Bill Hunt、Mike Keaveney、Brendan Daly、Paul O’Brien、Paul Mallon、Ian Collins、Sinead O’Keefe、Liam McCann、Patrick Walsh、Cristoir O’Reilly、Paul Laven、Samuel Landete、Niall Kearney和Mike Curtin。 團隊希望借此機會向ADI公司英國肯特分公司的Jon Strange和Ashish Shah,以及ADI公司西北實驗室(美國俄勒岡州比佛頓)的Fred Weiss致以誠摯的謝意,感謝他們提出的寶貴意見。

參考文獻

1. Mini-Circuits Corporation, VCO Designer’s Handbook, 1996.

Mini-Circuits公司,VCO Designer’s Handbook(VCO設計師手冊),1996年。

2. L.W. Couch, Digital and Analog Communications Systems, Macmillan Publishing Company, New York, 1990.

L.W. Couch,Digital and Analog Communications Systems(數(shù)字與模擬通信系統(tǒng)),Macmillan Publishing Company,New York,1990年。

3. P. Vizmuller, RF Design Guide, Artech House, 1995.

P. Vizmuller,RF Design Guide(RF設計指南),Artech House,1995年。

4. R.L. Best, Phase Locked Loops: Design, Simulation and Applications, 3rd Edition, McGraw-Hill, 1997.

R.L. Best,Phase Locked Loops: Design, Simulation and Applications(鎖相環(huán):設計、仿真與應用),第3版,McGraw-Hill,1997年。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。

推薦閱讀: