【導(dǎo)讀】為了解決FPGA的這一缺陷,制造商們一直都在苦苦找尋合適的方案,令人高興的是,伴隨工藝的不斷改進(jìn),兼具CPLD與FPGA優(yōu)點(diǎn)的芯片最終還是如期而至,被譽(yù)為“下一代非易失FPGA”的芯片是如何解決FPGA掉電易失難題的?

CPLD與FPGA雖然都?xì)w屬于可編程ASIC器件,但因?yàn)榻Y(jié)構(gòu)上的差異,CPLD使用起來要比FPGA方便很多。CPLD編程采用的是E2PROM或FASTFLASH技術(shù),無需外部存儲芯片,而FPGA則以高集成、靈活性著稱,局限是編程信息需存放在外部存儲器上,容易出現(xiàn)掉電數(shù)據(jù)丟失等缺陷。

為了解決FPGA的這一缺陷,制造商們一直都在苦苦找尋合適的方案,令人高興的是,伴隨工藝的不斷改進(jìn),兼具CPLD與FPGA優(yōu)點(diǎn)的芯片最終還是如期而至——恰逢Altera公司進(jìn)入中國市場三十周年之際,也是該系列芯片的第十代產(chǎn)品,這款被譽(yù)為“下一代非易失FPGA”的芯片被Altera命名為“MAX10 FPGA”。

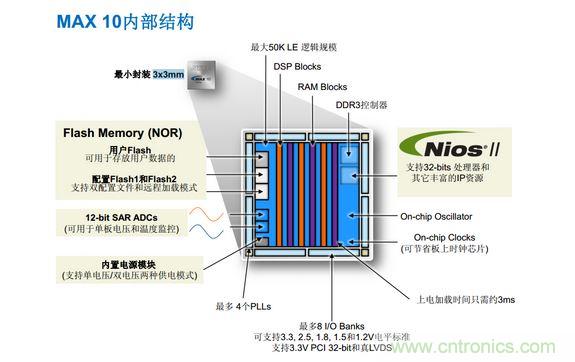

MAX10與傳統(tǒng)的FPGA芯片相比有何不同之處?Altera給出的答案為這是業(yè)界第一款多功能、低成本、單芯片F(xiàn)PGA,其最大的特點(diǎn)是內(nèi)部集成了兩個嵌入式閃存單元,無需添加外部RAM和存儲器件,當(dāng)系統(tǒng)發(fā)生故障時,數(shù)據(jù)會自動保存在其中一個鏡像單元中,避免出現(xiàn)系統(tǒng)失效等風(fēng)險。此外,由于MAX10采用的是臺積電55nm嵌入式NOR閃存技術(shù),支持瞬時接通功能,上電接通時間只需短短的3ms,這一性能相比以往的FPGA器件顯然要優(yōu)秀許多。

另一點(diǎn)值得注意的是,MAX10將過去常用在FPGA系統(tǒng)的32位核心處理器換成了Altera的軟核處理器Nios II,加上精度高達(dá)12bit的SAR ADC和溫度傳感器等外圍器件,可以為電路板設(shè)計減小接近50%的面積,同時也能大幅度降低BOM成本。

應(yīng)用方面,與傳統(tǒng)FPGA芯片類同,Altera將MAX10定位在工業(yè)、汽車、通信、計算和存儲等領(lǐng)域,只是由于全新的雙配置閃存和嵌入式處理軟核,可以在單芯片上實(shí)現(xiàn)大多數(shù)應(yīng)用中的失效安全遠(yuǎn)程更新和運(yùn)動控制處理的功能,借助MAX10內(nèi)置的DSP模塊,用戶也能夠編寫精準(zhǔn)的算法以應(yīng)對高性能、高精度的應(yīng)用場景。

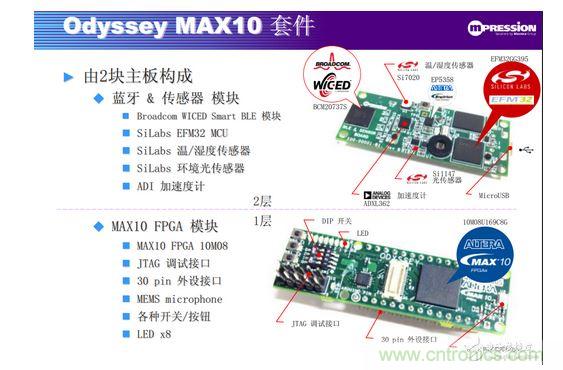

事實(shí)上,Max10早于去年9月份就發(fā)布了第一款新品,計劃是今年實(shí)現(xiàn)量產(chǎn)。此次Altera發(fā)布的不僅僅是與其配套的通用開發(fā)套件,更有Altera合作的分銷商駿龍科技帶來的兩款基于MAX10的特色方案,分別針對當(dāng)下十分火熱的物聯(lián)網(wǎng)以及電機(jī)驅(qū)動應(yīng)用。其中,Mpression Odyssey(奧德賽)是一個為物聯(lián)網(wǎng)應(yīng)用量身定制的開發(fā)和評估套件,用戶可以在iOS和Andriod手機(jī)上安裝專用的應(yīng)用程序,直接通過藍(lán)牙接口讀寫數(shù)據(jù)、分析數(shù)據(jù)和遠(yuǎn)程控制。

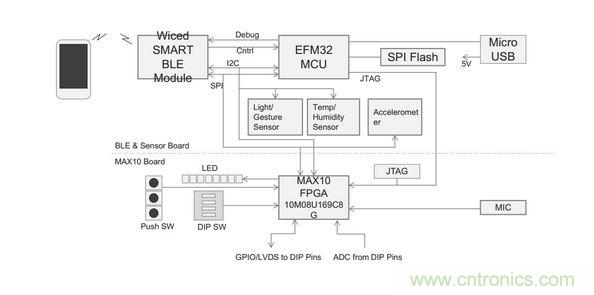

據(jù)駿龍科技方面介紹,“奧德賽(Odyssey)”開發(fā)套件主要由兩塊主板構(gòu)成:一塊MAX 10 FPGA板卡和一塊藍(lán)牙及傳感器板卡。MAX 10 FPGA板卡以Altera的MAX10為核心,帶有30個插針的擴(kuò)展接口、紐扣電池接口、JTAG調(diào)試接口、各種開關(guān)/按鈕和8個LED。藍(lán)牙及傳感器板集成了一個藍(lán)牙4.0模塊、一個32位處理器、溫度/濕度傳感器、紫外線/光敏/距離傳感器和加速度傳感器,用戶可以在手機(jī)應(yīng)用程序中進(jìn)行個性化的設(shè)置,從而快速體驗(yàn)MAX 10和傳感器的各種特性。

Odyssey 系統(tǒng)框圖

[page]

使用Odyssey套件的設(shè)計流程

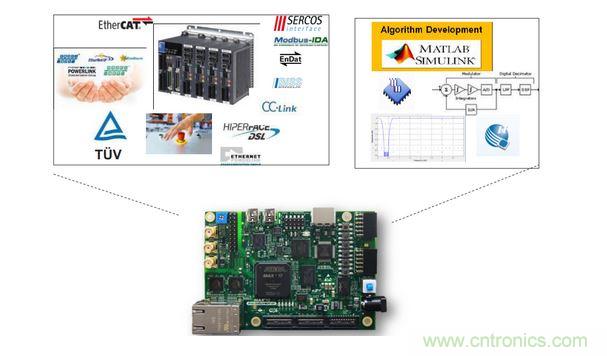

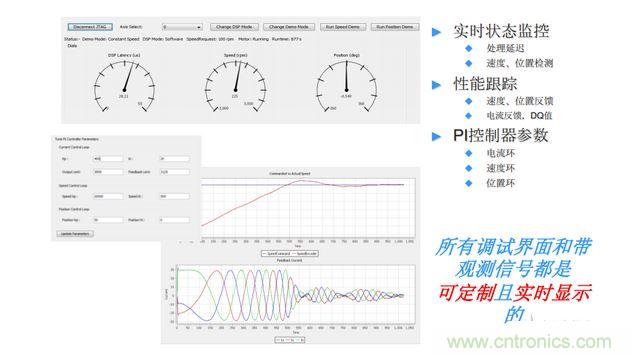

另一款基于MAX 10的電機(jī)驅(qū)動方案,使用FPGA替代傳統(tǒng)的CPU/DSP架構(gòu)實(shí)現(xiàn)算法,意味著所有的算法都將通過硬件實(shí)現(xiàn),這樣由于處理能力限制而在CPU中無法實(shí)現(xiàn)的算法,現(xiàn)在都可以在MAX 10 FPGA中以輕松地實(shí)現(xiàn)。Altera的MAX 10支持EtherCAT、Powerlink、Mechatrolink等工業(yè)以太網(wǎng)接口以及Endat 2.2, BISS等編碼器接口,用戶可以該方案中實(shí)現(xiàn)靈活可定制的接口。該方案還提供可定制的調(diào)試界面,客戶可以根據(jù)自己的需求,定制自己的調(diào)試界面,實(shí)時觀測內(nèi)部信號。

完善的MAX10電機(jī)設(shè)計平臺

可定制的實(shí)時控制調(diào)試界面