【導(dǎo)讀】高通道密度數(shù)據(jù)采集系統(tǒng)用于醫(yī)療成像�、工業(yè)過(guò)程控制����、自動(dòng)測(cè)試設(shè)備和40G/100G光通信系統(tǒng)可將眾多傳感器的信號(hào)多路復(fù)用至少量ADC��,隨后依序轉(zhuǎn)換每一通道����。 多路復(fù)用可讓每個(gè)系統(tǒng)使用更少的ADC���,大幅降低功耗、尺寸和成本���。 逐次逼近型ADC——通常根據(jù)它們的逐次逼近型寄存器而稱它們?yōu)镾AR ADC——具有低延遲特性��,因此適合用于要求對(duì)滿量程輸入階躍(最差情況)作出快速響應(yīng)而無(wú)任何建立時(shí)間問(wèn)題的多路復(fù)用系統(tǒng)��。 易于使用的SAR ADC提供低功耗和小尺寸�����。 本文重點(diǎn)討論與使用高性能精密SAR ADC的多路復(fù)用數(shù)據(jù)采集系統(tǒng)相關(guān)的關(guān)鍵設(shè)計(jì)考慮因素���、性能結(jié)果和應(yīng)用挑戰(zhàn)。

多路復(fù)用數(shù)據(jù)采集系統(tǒng)挑戰(zhàn)

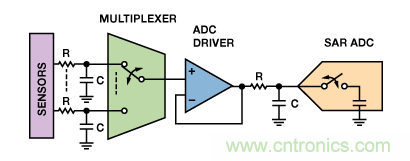

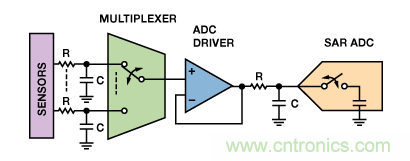

多路復(fù)用數(shù)據(jù)采集系統(tǒng)要求采用寬帶放大器����,以便驅(qū)動(dòng)ADC的滿量程(FS)輸入范圍時(shí)可以快速建立。 此外,對(duì)多路復(fù)用通道進(jìn)行開(kāi)關(guān)和順序采樣必須與ADC轉(zhuǎn)換周期同步�����。 相鄰輸入之間的巨大電壓差使這些系統(tǒng)易受通道間串?dāng)_的影響����。 為了避免產(chǎn)生誤差,完整的信號(hào)鏈(包括多路復(fù)用器和放大器)必須建立至所需精度——一般以串?dāng)_誤差或建立誤差表示�����。 圖1顯示的是一個(gè)數(shù)據(jù)采集系統(tǒng)框圖�,該系統(tǒng)包括多路復(fù)用器、ADC驅(qū)動(dòng)器和SAR ADC��。

圖1. 多路復(fù)用數(shù)字采集系統(tǒng)框圖

多路復(fù)用器

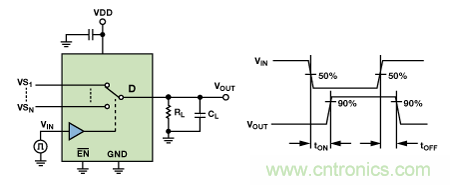

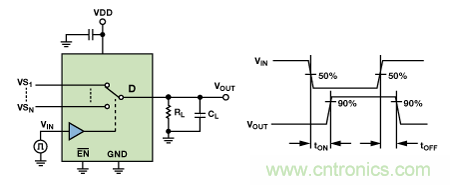

多路復(fù)用器的快速輸入切換和寬帶寬性能是實(shí)現(xiàn)高性能的關(guān)鍵�����。 多路復(fù)用器的開(kāi)啟或關(guān)斷時(shí)間表示應(yīng)用數(shù)字控制輸入與輸出超過(guò)VOUT 90%之間的延遲���,如圖2所示���。

圖2. 典型多路復(fù)用器的開(kāi)關(guān)時(shí)間

當(dāng)多路復(fù)用器切換通道時(shí)���,在其輸入端會(huì)產(chǎn)生電壓毛刺或反沖。 該反沖與開(kāi)啟和關(guān)斷時(shí)間�、導(dǎo)通電阻以及負(fù)載電容成函數(shù)關(guān)系。 具有低導(dǎo)通電阻的大開(kāi)關(guān)通常需采用大輸出電容�����,而每次輸入端開(kāi)關(guān)時(shí)�,都必須將其充電至新電壓����。 如果輸出未能建立至新電壓,則將產(chǎn)生串?dāng)_誤差���。 因此���,多路復(fù)用器帶寬必須足夠大,且多路復(fù)用器輸入端必須使用緩沖放大器或大電容�,才能建立至滿量程階躍。 此外���,流過(guò)導(dǎo)通電阻的漏電流將產(chǎn)生增益誤差�����,因此這兩者都應(yīng)盡可能小���。

ADC驅(qū)動(dòng)器

開(kāi)關(guān)多路復(fù)用器的輸入通道時(shí)����,ADC驅(qū)動(dòng)放大器必須在指定的采樣周期內(nèi)建立一個(gè)大電壓階躍����。 輸入可從負(fù)滿量程變化到正滿量程,也可能從正滿量程變化到負(fù)滿量程����,因此短時(shí)間內(nèi)可創(chuàng)建大輸入電壓階躍。 放大器必須具備較寬的大信號(hào)帶寬和較快的建立時(shí)間���,才能處理該階躍�。 此外��,壓擺率或輸出限流會(huì)導(dǎo)致非線性特征���。 同時(shí)��,驅(qū)動(dòng)放大器必須建立反沖——該反沖是由于采集周期開(kāi)始時(shí)����,SAR ADC輸入端的充電再平衡所導(dǎo)致。 這可能會(huì)成為多路復(fù)用系統(tǒng)中輸入建立的瓶頸��。 通過(guò)降低ADC的吞吐速率可緩解建立時(shí)間問(wèn)題�����,提供更長(zhǎng)的采集時(shí)間�,從而允許放大器有充分時(shí)間建立至所需精度。

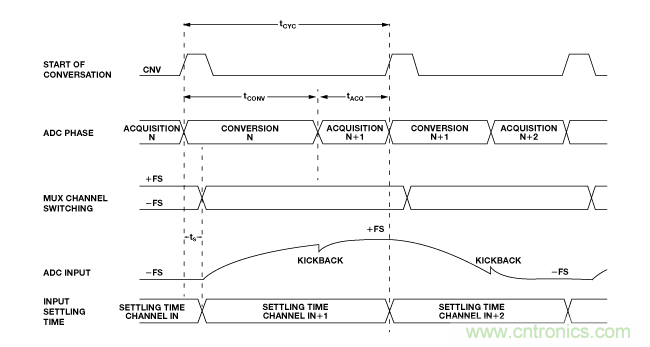

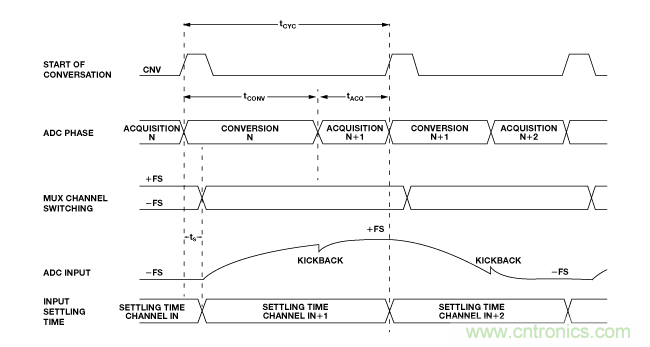

圖3顯示輸入端發(fā)生滿量程變化時(shí)��,多路復(fù)用數(shù)據(jù)采集系統(tǒng)的時(shí)序圖���。 ADC周期時(shí)間由轉(zhuǎn)換時(shí)間和采集時(shí)間構(gòu)成 (tCYC = tCONV + tACQ),其在數(shù)據(jù)手冊(cè)中通常指定為1/吞吐速率���。 轉(zhuǎn)換開(kāi)始時(shí)�,SAR ADC的電容DAC與輸入斷開(kāi)連接���,且多路復(fù)用器通道可在一個(gè)較短的開(kāi)關(guān)延遲時(shí)間tS之后切換到下一通道���。 這樣���,便可有盡可能多的時(shí)間來(lái)建立至選定通道。 為了保證最大吞吐速率下的性能�����,多路復(fù)用系統(tǒng)中的所有元器件都必須在多路復(fù)用器切換和采集時(shí)間結(jié)束之間這段時(shí)間內(nèi)完成ADC輸入端的建立��。 多路復(fù)用器通道開(kāi)關(guān)必須與ADC轉(zhuǎn)換時(shí)間正確同步���。 多路復(fù)用系統(tǒng)可實(shí)現(xiàn)的吞吐速率等于單一ADC吞吐速率除以采樣通道數(shù)�。

圖3. 多路復(fù)用數(shù)據(jù)采集系統(tǒng)典型時(shí)序圖

多路復(fù)用器輸入端的RC濾波器

某些設(shè)計(jì)人員使用低輸出阻抗緩沖器處理來(lái)自多路復(fù)用器輸入端的反沖���。 SAR ADC的輸入帶寬(幾十MHz)和ADC驅(qū)動(dòng)器的輸入帶寬(幾十到幾百M(fèi)Hz)高于采樣頻率��,且所需的輸入信號(hào)帶寬通常為幾十到幾百kHz范圍內(nèi)�,因此多路復(fù)用器輸入端可能需使用RC抗混疊濾波器��,以防干擾信號(hào)(混疊)折回目標(biāo)帶寬��,并緩解建立時(shí)間問(wèn)題���。 每個(gè)輸入通道使用的濾波器電容值都應(yīng)根據(jù)下列權(quán)衡條件仔細(xì)選擇: 大電容有助于衰減來(lái)自多路復(fù)用器的反沖�����,但大電容也會(huì)降低之前放大器級(jí)的相位裕量�,使其不穩(wěn)定。 對(duì)于高Q���、低溫度系數(shù)以及各種電壓下電氣特性穩(wěn)定的RC濾波器����,建議采用C0G或NP0類電容�����。 應(yīng)選用合理的串聯(lián)電阻值�����,以保持放大器穩(wěn)定并限制其輸出電流�����。 電阻值不可過(guò)高����,否則多路復(fù)用器反沖后放大器將無(wú)法對(duì)電容再充電。

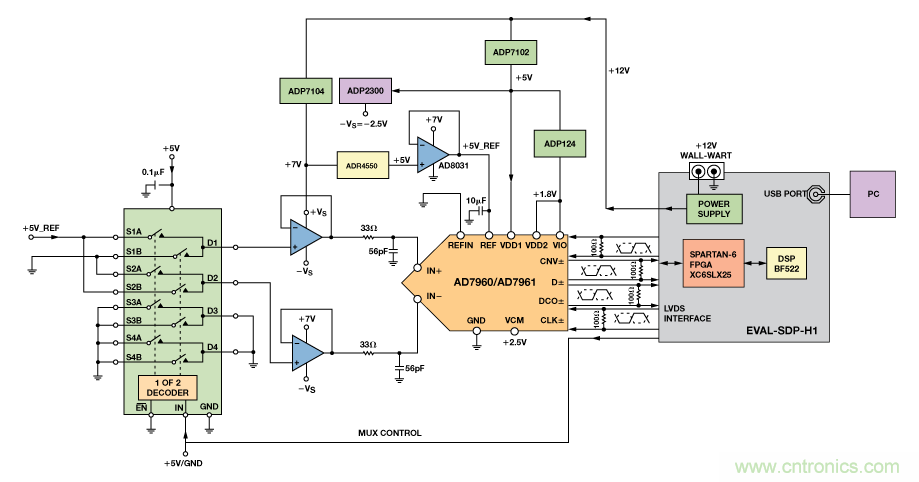

多路復(fù)用數(shù)據(jù)采集信號(hào)鏈

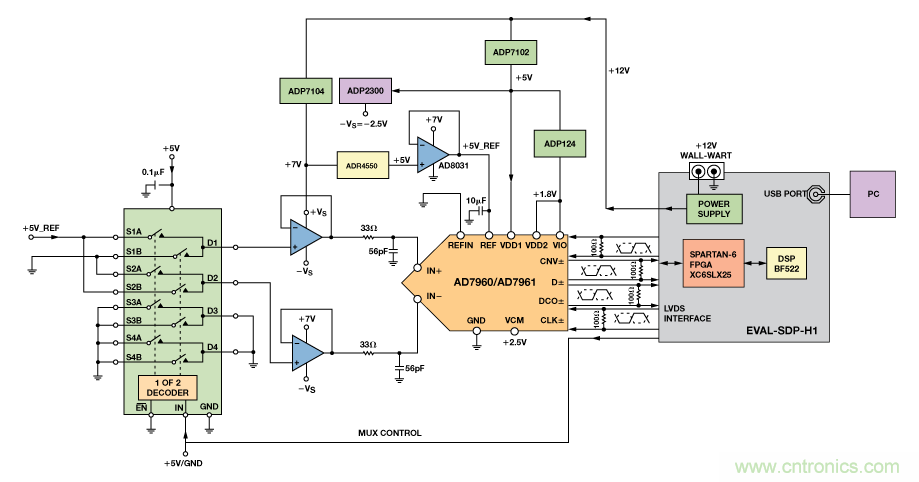

圖4顯示多路復(fù)用數(shù)據(jù)采集系統(tǒng)的簡(jiǎn)化信號(hào)鏈����。 采用 ADG774 ADG774 CMOS多路復(fù)用器來(lái)選擇兩個(gè)差分通道之一。 若要評(píng)估此系統(tǒng)����,可連續(xù)開(kāi)關(guān)ADG774的正負(fù)差分輸入,以產(chǎn)生滿量程階躍����。 兩個(gè)超低失真運(yùn)算放大器 ADA4899-1 緩沖多路復(fù)用器輸出,并驅(qū)動(dòng)18位�、5 MSPS PulSAR® ADC AD7960 RC濾波器(33 Ω/56 pF)有助于減少來(lái)自AD7960容性DAC輸入端的反沖,并限制進(jìn)入AD7960輸入端的噪聲���。

圖4. 多路復(fù)用數(shù)據(jù)采集系統(tǒng)簡(jiǎn)化信號(hào)鏈

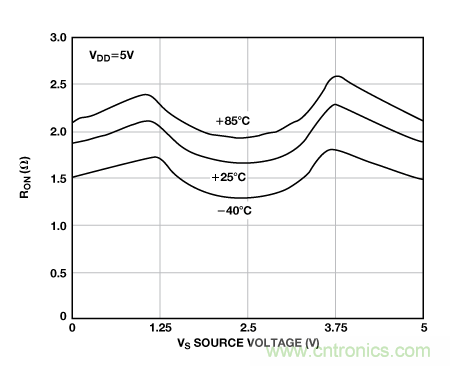

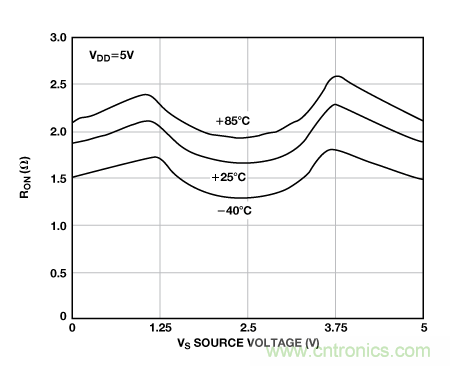

四通道2:1 CMOS多路復(fù)用器ADG774具有快速開(kāi)關(guān)速度(tON = 7 ns, tOFF = 4 ns)��、低導(dǎo)通電阻(RON = 2.2 Ω), �����、寬帶寬(f–3dB = 240 MHz)以及低功耗(5 nW)����,是便攜式和電池供電型儀器儀表的理想之選。 ADG774的輸入端連接5 V固定基準(zhǔn)電壓源和地�,從而輸出應(yīng)從正滿量程擺動(dòng)到負(fù)滿量程。 圖5顯示典型的導(dǎo)通電阻與輸入電壓關(guān)系曲線�����,該曲線輸入電壓范圍為完整的0 V至5 V模擬輸入����,溫度范圍為–40°C至+85°C。 該性能水平可確?��?焖匍_(kāi)關(guān)信號(hào)時(shí)擁有出色的線性度和低失真性能�。

圖5. ADG774導(dǎo)通電阻與輸入電壓的關(guān)系

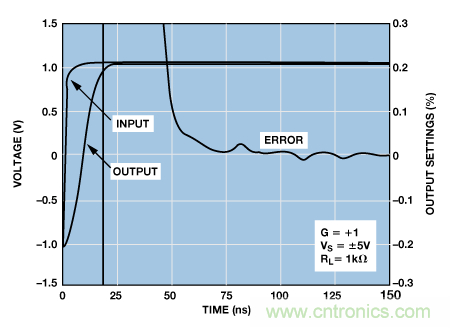

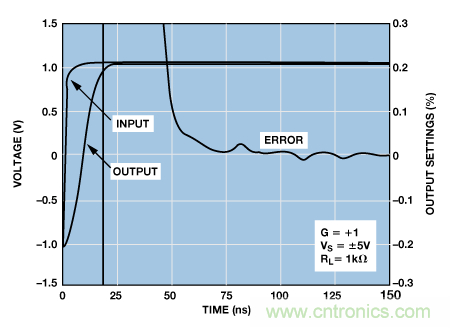

ADG774的輸出連接至高輸入阻抗放大器級(jí)���。 ADA4899-1高速運(yùn)算放大器具有超低噪聲(1 nV/√Hz)和超低失真(−117 dBc)��、600 MHz帶寬以及310 V/μs壓擺率性能。 該器件采用+7 V和−2.5 V電源供電����,具有足夠的裕量實(shí)現(xiàn)低系統(tǒng)噪聲和失真�����。 如圖6所示�,在2 V p-p輸入信號(hào)時(shí)�,放大器的0.1%建立時(shí)間為50 ns,是驅(qū)動(dòng)AD7960的理想之選����。

圖6. ADA4899-1典型建立時(shí)間

精密差分ADC AD7960具有同類一流的噪聲和線性度性能,無(wú)延遲或流水線延遲�,提供高精度(18位分辨率、±0.8 LSB INL���、99 dB SNR和–117 dB THD)����、快速采樣(5 MSPS)��、低功耗和低成本特性��。 該器件采用+5 V (VDD1)和+1.8 V(VDD2和VIO)電源供電����,以回波時(shí)鐘模式轉(zhuǎn)換時(shí)的功耗僅為46.5 mW (5 MSPS)���。 其內(nèi)核功耗隨吞吐速率線性變化,因此非常適合低功耗���、高通道密度應(yīng)用���。 可以利用低噪聲LDO(比如源。ADP7104和ADP124)產(chǎn)生5 V和1.8 V電源����。

該ADC的滿量程差分輸入范圍通過(guò)外部基準(zhǔn)電壓源設(shè)為5 V或4.096 V。 若要充分利用動(dòng)態(tài)范圍����,則輸入信號(hào)必須從0擺動(dòng)到VREF。 在該信號(hào)鏈中���,5 V基準(zhǔn)電壓由高精度(±0.02%最大初始誤差)��、低功耗(950 µA最大工作電流)基準(zhǔn)電壓源ADR4550提供�,該基準(zhǔn)電壓源具有出色的溫度穩(wěn)定性和低輸出噪聲�。 軌到軌運(yùn)算放大器AD8031緩沖外部基準(zhǔn)電壓����。 該器件具有大容性負(fù)載穩(wěn)定性��,可驅(qū)動(dòng)去耦電容����,以便最大程度降低瞬態(tài)電流引起的尖峰���。 AD8031適合從寬帶寬電池供電系統(tǒng)到低功耗�����、高器件密度�、高速系統(tǒng)的各種應(yīng)用����。

AD7960數(shù)字接口采用低壓差分信號(hào)(LVDS),具有自時(shí)鐘模式和回波時(shí)鐘模式����,提供ADC和數(shù)字主機(jī)之間高達(dá)300 MHz(CLK±和D±)的高速數(shù)據(jù)傳輸。 LVDS接口允許多個(gè)器件共享時(shí)鐘���,從而降低數(shù)字線路的數(shù)量��,并簡(jiǎn)化信號(hào)路由�。 相比并行接口它具有更低的功耗,因此在多路復(fù)用應(yīng)用中尤為有用�����。

AD7960在轉(zhuǎn)換開(kāi)始后大約115 ns內(nèi)返回采集模式�����,采集信號(hào)的時(shí)間約為200 ns總周期時(shí)間的40%�。 這一相對(duì)較長(zhǎng)的采集時(shí)間減輕了放大器的帶寬負(fù)擔(dān)并降低了建立時(shí)間要求,使得差分輸入更易于驅(qū)動(dòng)�����。 5 MSPS吞吐速率允許多個(gè)通道以高掃描速率進(jìn)行多路復(fù)用�����,因此高通道數(shù)系統(tǒng)所需的ADC數(shù)量更少��。

轉(zhuǎn)換期間����,AD7960的靜態(tài)時(shí)間要求為90 ns至110 ns�����,期間多路復(fù)用器輸入不可切換。 因此�,為了避免破壞正在進(jìn)行中的轉(zhuǎn)換,必須在CNV±起始信號(hào)上升沿后不足90 ns或超過(guò)110 ns時(shí)切換外部多路復(fù)用器����。 如果在此靜態(tài)期間切換模擬輸入,則最多可破壞15 LSB的當(dāng)前轉(zhuǎn)換���。 應(yīng)當(dāng)盡可能早地切換模擬輸入�,從而有盡可能多的時(shí)間來(lái)擺動(dòng)滿量程信號(hào)并建立輸入���。

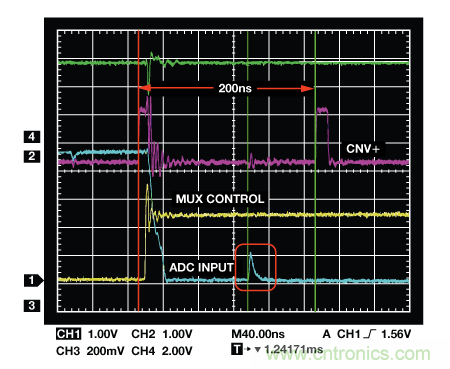

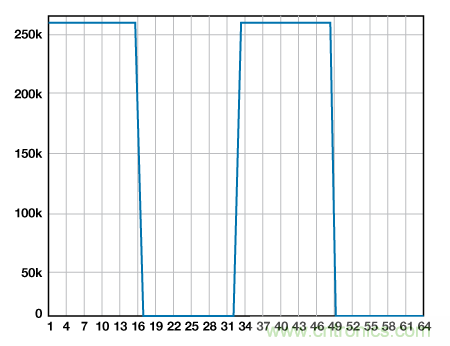

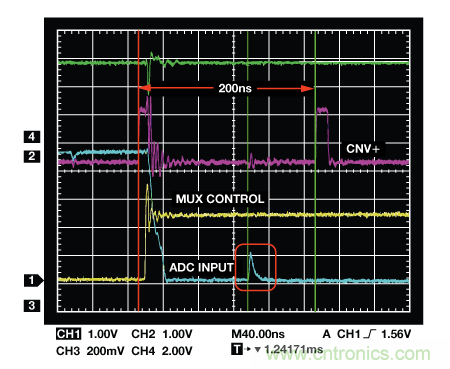

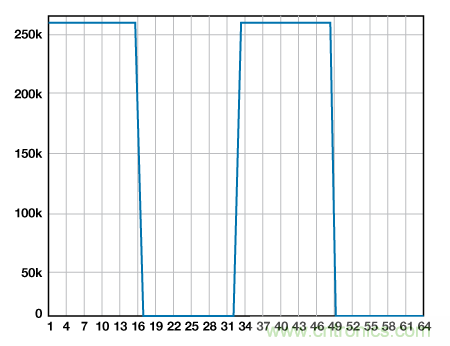

每16次轉(zhuǎn)換之后�����,多路復(fù)用器將在CNV±上升沿過(guò)后�����,于–5 V和+5 V之間開(kāi)關(guān)大約10 ns����,如圖7所示。這樣會(huì)產(chǎn)生滿量程差分階躍�,因此ADC輸出從負(fù)滿量程變?yōu)檎凉M量程,如圖8所示��。

圖7. 示波器曲線顯示來(lái)自內(nèi)部CAP DAC的反沖

圖8. AD7960輸出顯示ADG774在每16次轉(zhuǎn)換過(guò)后開(kāi)關(guān)

這一開(kāi)關(guān)時(shí)間延遲必須大于ADC的1.6 ns孔徑延遲�。 ADC輸入端測(cè)得的信號(hào)顯示來(lái)自AD7960中容性DAC的反沖約為1 V p-p(圖7,紅色高亮部分)�。 為了確保輸出完全建立,工作速率為5 MSPS時(shí)���,驅(qū)動(dòng)放大器必須在下一次轉(zhuǎn)換開(kāi)始前建立此瞬態(tài)���,即大約80 ns采樣時(shí)間內(nèi)。 以較低的吞吐速率運(yùn)行ADC可讓該反沖有更多的采集時(shí)間去建立��,從而多路復(fù)用器輸入通道之間的串?dāng)_誤差更低�,同時(shí)滿量程階躍建立時(shí)間性能更佳。

多路復(fù)用器輸入端測(cè)得的信號(hào)還顯示出來(lái)自通道開(kāi)關(guān)的反沖�����。 多路復(fù)用器輸入端的緩沖放大器有助于建立該反沖。 若由于成本或空間等原因無(wú)法使用輸入緩沖放大器�,則可在輸入端添加一個(gè)經(jīng)過(guò)優(yōu)化的RC濾波器,以降低反沖和串?dāng)_的影響��。 多路復(fù)用器輸入端使用的RC濾波器值會(huì)影響信號(hào)鏈的總噪聲和建立時(shí)間�。

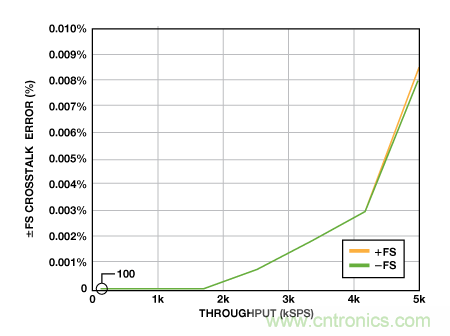

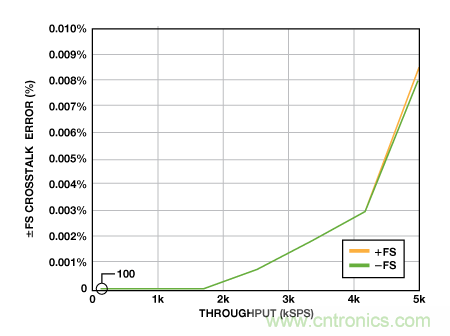

當(dāng)多路復(fù)用器靜止時(shí),AD7960運(yùn)行在5 MSPS最大吞吐速率下的數(shù)據(jù)采集系統(tǒng)輸出離開(kāi)正常滿量程約14 LSB��,可表示系統(tǒng)的總增益和失調(diào)誤差�。 對(duì)于大多數(shù)應(yīng)用而言��,該多路復(fù)用器開(kāi)關(guān)時(shí),ADA4899-1驅(qū)動(dòng)放大器有助于在可以接受的通道間串?dāng)_誤差范圍內(nèi)使輸出建立至正和負(fù)滿量程�。 輸出誤差與吞吐速率成指數(shù)關(guān)系���,并在5 MSPS時(shí)達(dá)到0.01%最大值,如圖9所示���。較低吞吐速率下的零串?dāng)_誤差表示ADC輸出在第一次轉(zhuǎn)換期間建立至其最終值��。

圖9. 串?dāng)_誤差與吞吐速率的關(guān)系�,以滿量程幅度的百分比表示

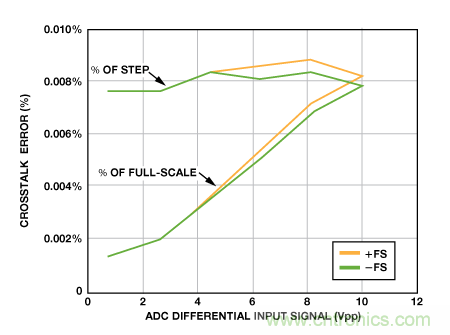

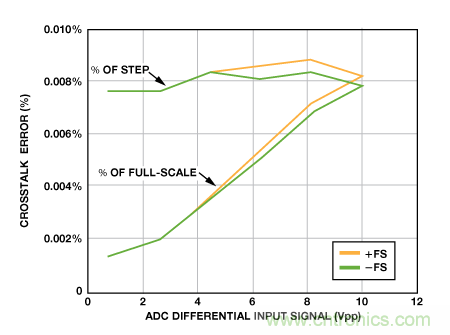

如圖10所示,1 V p-p(滿量程的10%)時(shí)���,相對(duì)于滿量程的串?dāng)_誤差不足0.001%��,并且隨差分輸入幅度成線性變化關(guān)系�。 相對(duì)于階躍幅度的串?dāng)_誤差在整個(gè)輸入范圍內(nèi)幾乎是平坦的�����,并且總是不足0.01%���。

圖10. 串?dāng)_誤差與差分輸入信號(hào)的關(guān)系

該多路復(fù)用信號(hào)鏈在噪聲與建立時(shí)間之間取得了最佳平衡�,具有最優(yōu)性能��。 這些結(jié)果表明����,建立大電壓階躍、從ADC輸入端反沖以及在多路復(fù)用操作中降低串?dāng)_誤差幅度時(shí)需要用到寬帶寬�����、快速建立放大器��。

多路復(fù)用數(shù)據(jù)采集系統(tǒng)布局考慮因素

印刷電路板(PCB)布局對(duì)于保持信號(hào)完整性以及實(shí)現(xiàn)信號(hào)鏈的預(yù)期性能至關(guān)重要。 圖11所示為69 mm × 85 mm四層評(píng)估板的頂視圖����。 在電路板上進(jìn)行獨(dú)立元器件和各種信號(hào)路由布局時(shí)必須十分仔細(xì)�����。 本例中,輸入信號(hào)從左至右進(jìn)行傳遞��。 ADC的全部電源和基準(zhǔn)電壓源引腳都必須采用電容去耦;電容應(yīng)靠近DUT放置���,并使用短而寬�、低阻抗的走線進(jìn)行連接,以便為高頻電流提供路徑、最大程度降低EMI的影響并減少電源線路上的毛刺效應(yīng)��。 數(shù)據(jù)手冊(cè)中建議的典型值為10 µF和100 nF。 多路復(fù)用器�����、放大器以及ADC的輸入和輸出引腳之下的接地層和電源層應(yīng)予以移除,以避免產(chǎn)生干擾寄生電容��。 器件的裸露焊盤應(yīng)使用多個(gè)過(guò)孔直接焊接到PCB的接地層上����。 將敏感模擬部分與數(shù)字部分相隔離����,同時(shí)使電源電路遠(yuǎn)離模擬信號(hào)路徑����。 快速開(kāi)關(guān)信號(hào)(比如CNV±或CLK±)不應(yīng)靠近或越過(guò)模擬信號(hào)路徑��,以防噪聲耦合至ADC。

圖11. 多路復(fù)用數(shù)據(jù)采集系統(tǒng)評(píng)估板頂層

多路復(fù)用數(shù)據(jù)采集應(yīng)用

工業(yè)自動(dòng)化和醫(yī)療成像中使用的高性能、多通道數(shù)據(jù)采集系統(tǒng)要求具有寬帶寬�����、高精度和快速采樣性能——所有這一切都必須 通過(guò)小尺寸����、低成本器件實(shí)現(xiàn)�。 18位AD7960和16位AD7961具有5 MSPS吞吐速率,允許更多通道多路復(fù)用至更少的ADC����,同時(shí)大幅降低成本���、功耗和封裝尺寸����。 這有助于設(shè)計(jì)人員應(yīng)對(duì)高通道密度系統(tǒng)中經(jīng)常遇到的空間��、散熱�����、功耗和其他重要設(shè)計(jì)挑挑戰(zhàn)���。

出色的線性度和低噪聲性能可提升計(jì)算機(jī)斷層掃描(CT)和數(shù)字X射線(DXR)應(yīng)用中的圖像質(zhì)量。 在高采樣速率下將眾多通道切換至較少的ADC可提供更短的掃描周期���,同時(shí)降低暴露在X射線下的劑量���,從而實(shí)現(xiàn)精確、成本合理的診斷以及更佳的患者體驗(yàn)���。 在CT掃描儀中�����,每通道使用一個(gè)積分器和采樣保持電路連續(xù)捕獲像素電流�����,并將輸出多路復(fù)用至高速ADC�。 低噪聲模擬前端將來(lái)自每個(gè)像素的小電流轉(zhuǎn)換為大電壓,然后再將電壓轉(zhuǎn)換為能夠處理的數(shù)字?jǐn)?shù)據(jù)�。

多路復(fù)用醫(yī)療成像系統(tǒng)——特別是CT和DXR——指定相鄰像素的典型像素間串?dāng)_誤差為±0.1%,而非相鄰像素的誤差為±0.01%�����。 本文所示結(jié)果表明��,本多路復(fù)用信號(hào)鏈在最大吞吐速率和滿量程范圍內(nèi)產(chǎn)生的串?dāng)_誤差仍處于可接受的限值之內(nèi)����。

結(jié)論

高性能、高通道密度��、多路復(fù)用數(shù)據(jù)采集系統(tǒng)要求具備可靠的性能����、靈活的功能以及高精度,同時(shí)還要滿足功耗�、空間和散熱要求。 本文提供根據(jù)關(guān)鍵設(shè)計(jì)考慮因素來(lái)選擇多路復(fù)用信號(hào)鏈元器件以實(shí)現(xiàn)預(yù)期性能的指南����,以及如何在吞吐速率�、建立時(shí)間和噪聲之間進(jìn)行權(quán)衡取舍����。 該信號(hào)鏈可實(shí)現(xiàn)最優(yōu)性能�,滿量程范圍內(nèi)的5 MSPS串?dāng)_誤差不超過(guò)0.01%。

推薦閱讀: