【導(dǎo)讀】DDR4是JEDEC組織關(guān)于DRAM器件的下一代標(biāo)準(zhǔn)。DDR4主要是針對(duì)需要高帶寬低功耗的場(chǎng)合�����。這些需求導(dǎo)致了DDR4芯片引入了一些新的特點(diǎn)���,這些新的特點(diǎn)���,導(dǎo)致在系統(tǒng)設(shè)計(jì)中,引入一些新的設(shè)計(jì)需求���。

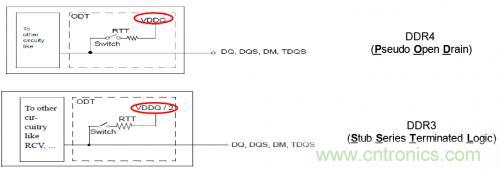

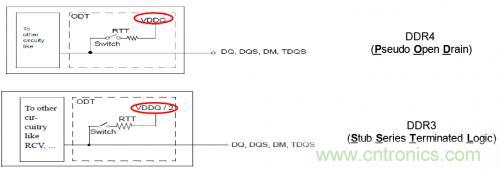

DDR4的I/O架構(gòu)稱為PSOD(Pseudo Open Drain)��,這個(gè)新的設(shè)計(jì)�,將會(huì)帶來接收端功耗的變化��,以及Vref電平的差異�����。接下來的將會(huì)討論P(yáng)SOD輸出和上一代DDR3標(biāo)準(zhǔn)的差異。

POD vs STLL

驅(qū)動(dòng)DRAM工業(yè)發(fā)展的一個(gè)主要市場(chǎng)需求是對(duì)內(nèi)存器件的低功耗要求�。介于這個(gè)原因,DDR4引入了一個(gè)新的IO驅(qū)動(dòng)標(biāo)準(zhǔn)���,成為PSOD(Pseudo Open Drain)�。在PSOD里��,接收端將信號(hào)端接到軌電壓(VDD)��,而不是軌電壓的一半(VDD/2)���。

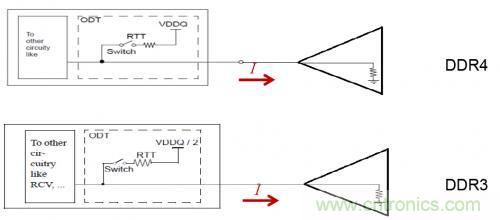

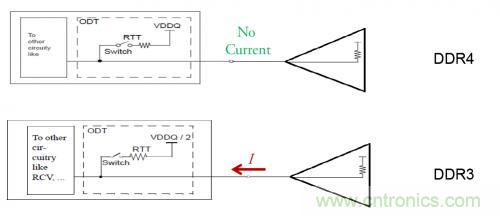

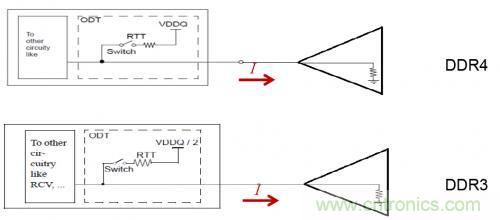

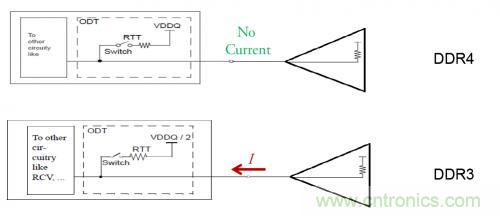

為了直觀的看出端接方式的差異對(duì)總的功耗的影響����,下面分別比較了在輸出高和低得情況下��,DDR4/DDR3的電流流向�����。

當(dāng)輸出為低時(shí)����,SSTL/POD的都會(huì)有電流流過��。實(shí)際上�,POD的拉電流會(huì)比SSTL稍大���,因?yàn)槠涠私拥能夒妷海鳶STL的端接到軌電壓的一般�。這個(gè)也是為什么DDR4的軌電壓選用了一個(gè)稍微低一點(diǎn)的電平。

主要的區(qū)別在于輸出高電平時(shí)��。SSTL電平將會(huì)繼續(xù)有消耗電流���,并且電流大小和輸出低電平的時(shí)候一致�����。POD在輸出高電平時(shí)�����,沒有工作電流���。

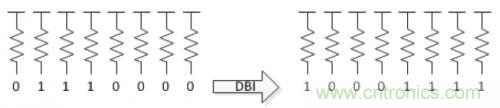

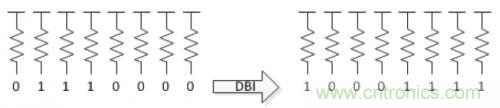

所以���,一個(gè)降低DDR4系統(tǒng)功耗的方法是,盡量加大DDR4輸出高的數(shù)量����。這個(gè)就是為什么DDR4中多了“DBI管腳”。舉個(gè)例子�����,當(dāng)8bit lane中有至少有5個(gè)DQ都是低時(shí)����,所有的Bit將會(huì)被翻轉(zhuǎn),并且DBI(Data Bus Inversion)置低����,用來指示數(shù)據(jù)線的反轉(zhuǎn)。通過這個(gè)方法���,總共9個(gè)信號(hào)中(8個(gè)DQ和1個(gè)DBI)�,總有至少5個(gè)是被驅(qū)動(dòng)為高電平���。如果原始的數(shù)據(jù)中有4個(gè)或者更多的信號(hào)被驅(qū)動(dòng)為高時(shí)�,那么DBI信號(hào)也將會(huì)設(shè)為高,同樣��,還是9個(gè)里面至少有5個(gè)為高����。這樣的話,在每一個(gè)數(shù)據(jù)傳輸?shù)倪^程中�����,都是至少有5/9的數(shù)據(jù)是高電平���,可以在一定程度上降低了功耗。