【導(dǎo)讀】以下是一位資深工程師分享關(guān)于Flyback電源各層面的分析與總結(jié),句句經(jīng)典!各位工程師千萬不要錯過......

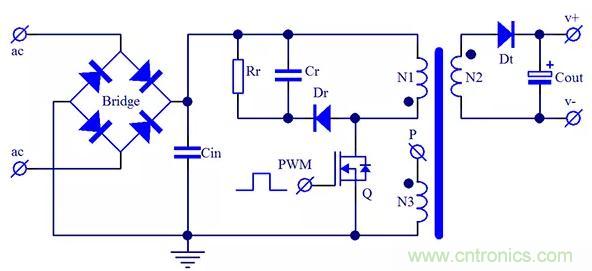

對于Flyback拓?fù)浣Y(jié)構(gòu)的詮釋......

Flyback的五之最

1)應(yīng)用最多的變換器

生產(chǎn)數(shù)量、人均擁有量、總用電容量?

2)性能最差的變換器

能效、電磁兼容性

3)工況最差的變換器

硬開關(guān)、電壓應(yīng)力、電流應(yīng)力、磁利用率、EMC應(yīng)力

4)任務(wù)最重的變換器

安規(guī)隔離、寬電壓應(yīng)用、PFC應(yīng)用,待機(jī)

5)最簡單的變換器

還有比它更簡單的隔離變換器?集成度越來越高、元件越來越少,做出來很容易,做好呢?

什么叫好?

●比別人做的好

●沒有比這個更好

●為什么我做的總沒別人做的好

●為什么有那么幾個人做出來的反激就是明顯比別人好

●我手上這個還能不能更好

●如果能證明這個不可能更好,那就是最好

開關(guān)電源很多指標(biāo):

效率、成本、安全、電磁兼容性、待機(jī)、能效、可靠性、穩(wěn)定性、保護(hù)、體積(功率密度)、超薄、精度、紋波、電壓調(diào)整率、負(fù)載調(diào)整率、交叉調(diào)整率、溫度、壽命、功率因數(shù)、總諧波。

好不好,看效率:

●效率做起來,才談得上其他的

●先做好效率,再說其余

●犧牲效率的設(shè)計(jì)不是好設(shè)計(jì)

●效率是一點(diǎn)一點(diǎn)摳出來的

●對效率的追求,永遠(yuǎn)是值得的

●多花點(diǎn)時間優(yōu)化效率,就是效率

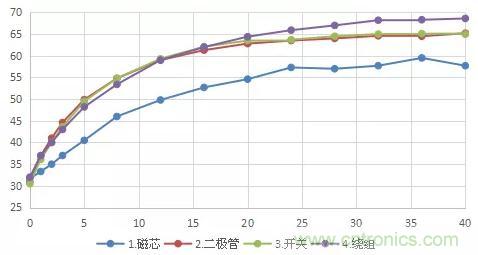

效率能做到多高呢?

●很多人以88%為標(biāo)準(zhǔn),幾年前的標(biāo)準(zhǔn)

●估計(jì)現(xiàn)在能批量出貨的應(yīng)該在90%以上,才有競爭力

●有的人輕易就能做到91、92%以上去

●還有個別人,一不小心就做到93%以上去

所謂高手:定一個設(shè)計(jì)標(biāo)桿:整機(jī)效率94%

●覺得太高?那就93%,不能再低了

●這是一個在特定情況下可以實(shí)現(xiàn)的整機(jī)效率

●這是一個難以實(shí)現(xiàn)的整機(jī)效率。

●即使沒能實(shí)現(xiàn),我們也應(yīng)該知道自己的差距

●即使沒能實(shí)現(xiàn),我們也應(yīng)該知道為什么沒能實(shí)現(xiàn),是哪些因素導(dǎo)致的

一、什么在影響反激的效率?

1.漏感

●漏感問題是反激變換器的基本問題。漏感是硬傷。要實(shí)現(xiàn)高效率,控制漏感是重頭戲。先做好漏感,再說其余。

●漏感有多大?意味著能量傳遞損失多大,變換器效率損失有多大,鉗位電路熱損耗有多大。這都是額外的,其他變換器沒有的。

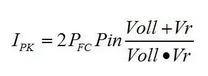

2.較大的峰值電流 Ipk

●反激的峰值電流較之其他拓?fù)涓?,原因是其儲?釋能這種間歇工作模式?jīng)Q定的,占空比較小。

●臨界模式、斷續(xù)模式、PFC控制、寬電壓應(yīng)用更加劇了峰值電流應(yīng)力。

●峰值電流決定一個反激變壓器的磁應(yīng)力,導(dǎo)致磁利用率較低。

●峰值電流還與開關(guān)(以及副邊二極管)導(dǎo)通損耗直接相對應(yīng)。

3.較高的原邊電壓應(yīng)力

●反激的原邊電壓應(yīng)力較之其他拓?fù)涓?,原因是反射電壓、漏感尖峰電壓疊加在輸入電壓上,導(dǎo)致開關(guān)電壓應(yīng)力為輸入電壓的1.5~2倍。

●導(dǎo)致:

a)硬開關(guān)動作的損耗劇增(因各種寄生電容導(dǎo)致的損耗增加2~4倍)

b)開關(guān)內(nèi)寄生二極管反向恢復(fù)電流激增(導(dǎo)致關(guān)斷損耗激增)。

c)必須使用耐壓高出1.5~2倍的開關(guān),其飽和壓降大幅度提高,導(dǎo)通損耗劇增。

4.更高的副邊二極管電壓應(yīng)力

●反激的副邊二極管電壓應(yīng)力更是增加得離譜,按市電AC/DC變換的典型參數(shù),這個電壓應(yīng)力更是高到了其輸出電壓的3到5倍,還可能有可觀的尖峰電壓疊加。

●導(dǎo)致:

a)二極管翻轉(zhuǎn)動作的損耗劇增(因各種寄生電容導(dǎo)致的損耗增加10~30倍)

b)二極管反向恢復(fù)電流激增(不要相信此處沒有反向恢復(fù)的說法)

c)必須使用耐壓高出輸出電壓幾倍的二極管,其飽和壓降大幅度提高,導(dǎo)通損耗劇增

二、拓?fù)洵h(huán)境層面的設(shè)計(jì)考慮

高效率的反激設(shè)計(jì)應(yīng)該比一般設(shè)計(jì)更注意仔細(xì)追究拓?fù)鋺?yīng)用環(huán)境,這是因?yàn)閷π实臉O限追求也是對其應(yīng)用環(huán)境的極限追求,要讓電路工作處于最明確、最舒適、最能揚(yáng)長避短、最能發(fā)揮到極限的環(huán)境。

1.選擇一個較軟的拓?fù)淇刂颇J?。?zhǔn)諧振(QR)模式是首選,而CCM、CRM模式可能效率較低。其他諸如諧振模式、無損鉗位模式、Sepic模式等,由于技術(shù)尚不成熟一般不予考慮。

2.輸出電壓較低時,副邊考慮同步整流是好主意。

3.盡量考慮采用專用控制芯片、有口碑的芯片、原邊控制的芯片。避免使用6562、3842這樣的通用芯片去做反激,用一大堆運(yùn)放達(dá)成的控制環(huán)路更是不可取。不是因?yàn)檫@些芯片不能用,而是要伺候這些芯片是很難受的。

4.認(rèn)真論證你的最低輸入電壓,也就是最大峰值電流 Ipk 的取值。全電壓的必要性,過渡模式(CCM模式)的必要性,限流模式(OCP模式)的必要性,控制轉(zhuǎn)折點(diǎn)設(shè)置在哪里?任何時候都不要讓 Ipk 失控。開機(jī)沖擊和短路沖擊對 Ipk 的影響也要考慮。

5.認(rèn)真論證你的最高輸入電壓,市電AC/DC應(yīng)用按264Vac做顯然是有問題的,小區(qū)電壓飆到264Vac以上是經(jīng)常的。建議按277Vac(必要時再增加一點(diǎn)余量)考慮。

6.認(rèn)真論證你的最高輸出電壓,或者CV/CC模式的最大輸出功率。充分考慮各種情況下輸出電壓意外飆高的可能性,并選擇一款OVP嗨得住的芯片。OVP是否嗨得住,不僅涉及最高輸出電壓帶來的最高電壓應(yīng)力、功率應(yīng)力,還直接關(guān)乎假負(fù)載的損耗功率。最高輸出電壓就是脫離OVP保護(hù)模式后的第一個電壓。

三、電路運(yùn)行層面的設(shè)計(jì)考慮

1.輸入回路干凈利落,避免熱敏電阻、保險電阻的設(shè)計(jì),硅橋要電流稍大的。共模差模帶來的損耗要斤斤計(jì)較,一級兩級、個大個小、線粗線細(xì)之間的差別是很大的。這還涉及EMC設(shè)計(jì)水平,如何做到用最少的共模差模解決問題?

2.開關(guān)的選型,MOS最好是外置的,這樣方便選型和控制。內(nèi)阻(Rdson)盡量小一點(diǎn),Cool-MOSc也是可以的。最重要的是耐壓,市電 AC/DC 典型應(yīng)用,MOS 耐壓首選 650V 的,耐壓更低的應(yīng)該嗨不住,耐壓更高的特性急劇惡化,其價格、內(nèi)阻都是很難接受的。

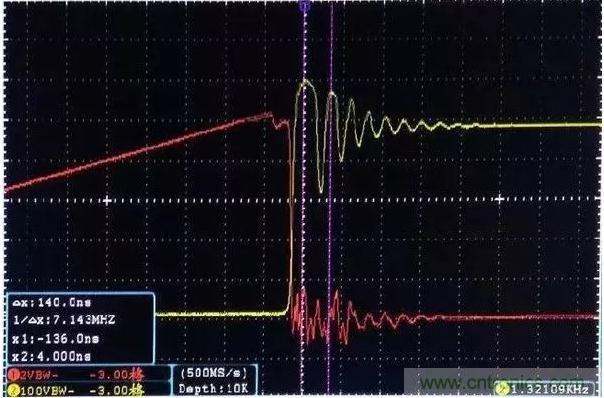

3.驅(qū)動能力要足夠,Rg下拉、上拉電阻要分開(上拉電阻與二極管并聯(lián)后串下拉電阻)。關(guān)斷要干凈利落,一定不能讓米勒平臺出現(xiàn)在 Ipk 位置。

4.在高壓端通過電阻實(shí)現(xiàn)的電壓采樣、VCC啟動、線電壓補(bǔ)償、安規(guī)電容放電等電路是要耗電的。副邊假負(fù)載、副邊采樣控制電路也是要耗電的。這些電路要優(yōu)化,其能耗要追究。

5.最敏感的電流采樣、過零(谷底)采樣、FB采樣電路要精心布置,電路要簡潔,阻抗要匹配,雜散參數(shù)影響要小,PCB要安靜。這是因?yàn)楦咝孰娐穼@些細(xì)微的控制有更高的要求,不能出問題。

6.各部波形要正常,沒有奇怪的、離譜的東西。環(huán)路、高PFC電路的主要參數(shù)要調(diào)試好,主要指標(biāo) PF 和 THD 要基本達(dá)到要求,工作穩(wěn)定,不能有振蕩,在這個前提下做的效率優(yōu)化才有意義。

7.在最后優(yōu)化效果出來前,(在經(jīng)驗(yàn)不足時)某些要影響效率的次要電路可以先裸奔。比如:磁珠要取消、DS上并聯(lián)的電容要取消、差模共??啥搪?、鉗位功率最小化(降低電壓運(yùn)行看情況)、副邊二極管吸收電路不連接(用高耐壓二極管先代替看情況)、假負(fù)載功率最小化,CS采樣電阻最小化(非OCP模式),甚至VCC供電和副邊控制電路用電可考慮用電池組臨時供電。以免這些電路的設(shè)置不合理影響主電路運(yùn)行工況,造成誤判。

四、變壓器設(shè)計(jì)

高效率反激變換器大部分設(shè)計(jì)技巧隱藏在變壓器里,繞組結(jié)構(gòu)和磁決定變壓(換)器性能是繞組結(jié)構(gòu)在決定運(yùn)行參數(shù)。

1.繞組結(jié)構(gòu)的約束條件:

●窗口約束

原邊副邊窗口分配用銅量大致相等,滿足幾何和能量的大致對應(yīng)。技巧是分配要合理、線包要基本飽滿。

●三明治約束

二夾一的意思,是降低漏感的重要措施,技巧是減少EMC結(jié)構(gòu)、安規(guī)結(jié)構(gòu)的不利影響,耦合要緊密。還需注意氣隙對繞組的影響、磁芯作為導(dǎo)體的影響,輔助繞組的結(jié)構(gòu)和位置。

●整層約束

是降低漏感最重要的措施,技巧是無論如何都要整層密繞、少半匝都不行,均繞不行、半層更不行,匝數(shù)太少就雙線或多線并繞、或者用與槽寬等寬的銅箔疊繞。

繞組結(jié)構(gòu)設(shè)計(jì)可以歸結(jié)為平面幾何問題。設(shè)計(jì)目標(biāo)是漏感最小化、氣隙最小化,需要較多的經(jīng)驗(yàn)、技巧、時間、智慧、精力才能達(dá)成。是反激變換器設(shè)計(jì)的重點(diǎn),也是高效率反激設(shè)計(jì)的關(guān)鍵所在。漏感的設(shè)計(jì)標(biāo)桿:1%,否則不能實(shí)現(xiàn)高效率。

2.繞組結(jié)構(gòu)決定運(yùn)行參數(shù):

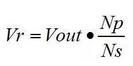

●一個繞組結(jié)構(gòu)最終與原邊副邊匝數(shù)相對應(yīng),其匝比決定反射電壓 :

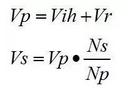

●反射電壓決定原邊MOS和副邊二極管電壓應(yīng)力(不含尖峰部分):

● 有了反射電壓即可算出原邊電流應(yīng)力:

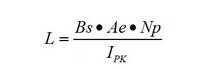

●由此得到原邊電感量:

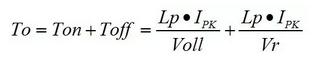

●基于臨界模式的最大PWM特征周期:

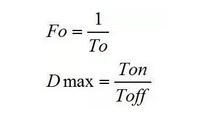

●與之對應(yīng)的最低特征頻率和最大占空比:

3.磁參數(shù)優(yōu)化:

1)磁芯選擇

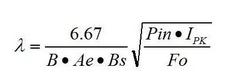

給出一個(PC40材質(zhì)的)磁功率應(yīng)力的經(jīng)驗(yàn)公式:

●可由此大致判斷(λ=1)磁芯是否合適。高效率的設(shè)計(jì)要求磁應(yīng)力不能太緊張,也就是變壓器(包括繞組和磁芯)的發(fā)熱不要成為整個電源最突出的。當(dāng)熱應(yīng)力突出時,應(yīng)增加磁芯的 Ae.B 或者使用更好的材質(zhì)。

磁芯型號也有影響,骨架槽寬 B 越大于槽深 H 的偏平窗口由于越容易滿足整層約束而更有利于減少漏感。

2)磁飽和強(qiáng)度Bs

優(yōu)化方向是Bs值最優(yōu)化,約束條件是磁芯品質(zhì),可按 Bs(或原邊電感量 Lp)擴(kuò)大20%~30%余量后 Ipk 波形可見臨界飽和跡象為判據(jù)確定Bs取值。更高的Bs取值,對應(yīng)更小的氣隙、更小的漏感,更小的尖峰電壓、可能更高的整機(jī)效率。但太高的Bs取值會使上述余量更小、磁芯的品質(zhì)控制困難、成品率降低。

Bs不能靠估計(jì),要實(shí)測。Bs有個最佳值,PC40材質(zhì),大約為0.3T,偏離這個最佳值都會降低效率。

4.運(yùn)行參數(shù)優(yōu)化:

1)匝比 Np/Ns,反射電壓 Vr

優(yōu)化方向是匝比和反射電壓最優(yōu)化,約束條件是原邊電壓應(yīng)力(即MOS管耐壓)。更大的匝比對應(yīng)更高的反射電壓Vr、更小的峰值電流 Ipk、可能更小的漏感、更大的最大占空比 Dmax、更低的副邊電壓應(yīng)力Vs(以便使用最低耐壓的肖特基)。但反射電壓太高會導(dǎo)致開關(guān)電壓應(yīng)力及開關(guān)損耗增加,抵消以上效應(yīng),應(yīng)適可而止。

2)原邊匝數(shù)Np

優(yōu)化方向是原邊匝數(shù)最優(yōu)化,約束條件是磁損和開關(guān)損耗。更少的原邊匝數(shù),對應(yīng)更小的氣隙、更小的漏感絕對值、更小的尖峰、更小原邊電感量 Lp、更高的特征頻率 Fo、更低的銅損、更大的磁損、更大的開關(guān)損耗、可能更高的輸入電壓低端效率、可能更低的輸入電壓高端效率。根據(jù)這些表現(xiàn),優(yōu)化到佳值。

五、電路優(yōu)化配合

一個好的變壓器設(shè)計(jì)出來以后,需要電路與之配合,才能充分發(fā)揮高效率特性。

1.鉗位電路

尖峰一定是有的,尖峰大小取決于漏感,鉗位功率也取決于漏感。鉗位二極管耐壓應(yīng)不低于MOS管耐壓,一般應(yīng)考慮用快恢復(fù)的。避免使用4007、磁珠、二極管上串電阻,這些東西是要發(fā)熱的。鉗位電阻應(yīng)與鉗位電容配合,考慮到漏感能量有一部分消耗在開關(guān)上,鉗位功率控制在漏感的50%以下為宜。

2.副邊二極管反壓尖峰 RC 吸收電路

非CCM模式,建議在原邊MOS驅(qū)動上動手腳,增加導(dǎo)通電阻、減緩導(dǎo)通速率、利用米勒效應(yīng)轉(zhuǎn)移功率、達(dá)成減小甚至完全消除副邊二極管反壓尖峰之目的。此法可完全省掉RC吸收,收獲最高整機(jī)效率。即使有過渡到CCM模式,上述導(dǎo)通電阻也應(yīng)做適應(yīng)性調(diào)整,采用一個合理取值,配合RC吸收達(dá)成目的。

RC吸收是有損吸收,對于每一個案例、每一個吸收電容值,都有一個最佳電阻值配合使尖峰最小化,找到這個電阻值,達(dá)成最小損耗的吸收。在多路輸出時,主要的回路才需要RC吸收(并按上面的方法使損耗最小化),次要的回路建議裸奔(用二極管耐壓去扛),或者稍微吸收一下即可,切不可喧賓奪主。

3.副邊二極管耐壓

在漏感最小化、吸收最佳配合后,副邊二極管電壓應(yīng)力已經(jīng)最小化了,按此電壓應(yīng)力選擇一款最低耐壓的肖特基,即達(dá)成最高效應(yīng)用。即使有同步整流助力也應(yīng)如此。此舉是提高整機(jī)效率最重要的措施之一。

六、其它電路優(yōu)化配合

1.副邊控制電路耗電最小化設(shè)計(jì) 盡量在 TL431(1~2mA)范圍內(nèi)解決問題,假負(fù)載電流、吸收回路電流亦可利用起來為其供電。避免單獨(dú)繞組供電的設(shè)計(jì)。

2.輔助繞組電壓最小化設(shè)計(jì) 以芯片VCC工況為準(zhǔn),電壓匹配、電流夠用即可,VCC電容容量夠用即可。能少一匝就少繞一匝的意思,避免為加快啟動而故意增加VCC電流的設(shè)計(jì)。

3.電流采樣電阻Rcs 可能成為PCB板上的熱點(diǎn),也就是損耗點(diǎn)。在必須采樣時,應(yīng)該糾結(jié)芯片的采樣閥值設(shè)置,盡量低一點(diǎn)有利效率;否則可適當(dāng)減小此電阻值,減小熱損失。

4.EMC最優(yōu)化設(shè)計(jì) 對高效率電源而言,EMC最優(yōu)化設(shè)計(jì)的另一個目的是簡化端口的差模共模工程,從而減少器件損耗、提高效率。這些措施是:

a、變壓器 EMC 結(jié)構(gòu)要追究、隔離屏蔽要做好

b、 PCB 要做好

c、 Y 電容要用兩只來湮滅偶極子噪音

d、開關(guān)導(dǎo)通速率宜緩不宜急

e、 共模差模結(jié)構(gòu)要合理

5.熱平衡設(shè)計(jì) 仔細(xì)考察電源的熱景象,主要溫升器件的極端最大溫升應(yīng)大致一致,一般可以50C°為限值。溫升還可判斷變壓器設(shè)計(jì)的合理性、散熱工的合理性、意外的溫升點(diǎn)意味著高效率設(shè)計(jì)的敗筆。