NMOS LDO工作簡(jiǎn)介

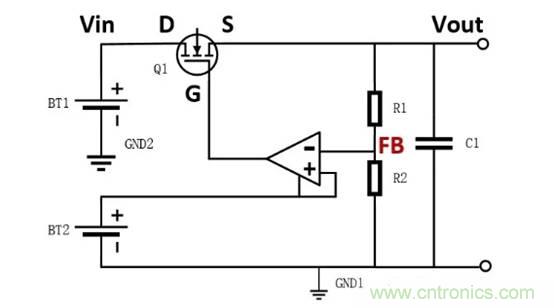

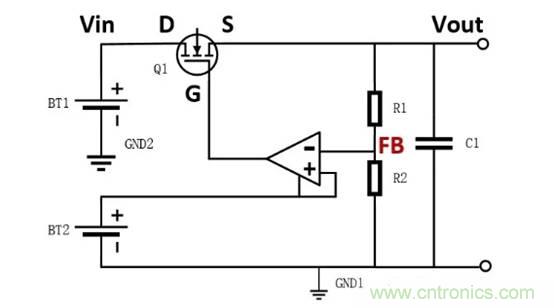

下圖是一個(gè)NMOS LDO的基本框圖����,NMOS LDO一般也工作在飽和區(qū)(特殊時(shí)會(huì)在可變電阻區(qū)),所以Vg要大于Vs�����,因此NMOS LDO除了有Vin引腳�����,一般還會(huì)有個(gè)Vbias引腳來(lái)給MOS G極提供高壓驅(qū)動(dòng)源��;或者只有一個(gè)Vin����,而內(nèi)部集成了CHARGE BUMP來(lái)為G極提供高壓驅(qū)動(dòng)源。大體工作流程同PMOS LDO:當(dāng)Vout下降時(shí),反饋回路中的Vfb也會(huì)下降����,誤差放大器輸出端Vg就會(huì)增加,隨著Vg增加���,Ids電流也增加�, 終使得Vout又恢復(fù)到原始電平���,狀態(tài)如下:

Vout↓-->Vfb↓-->Vg↑--Iout↑-->Vout↑

2. NMOS LDO詳細(xì)工作原理

下圖是某NMOS輸出特性曲線�����,讓我們結(jié)合上圖和下圖分析����,當(dāng)Vout下降��,Vin不變�����,則Vds=Vin-Vout����,Vds增加�����,MOS工作點(diǎn)由A轉(zhuǎn)移到B;緊接著反饋回路開(kāi)始工作�����,Vfb電壓減小�����,經(jīng)過(guò)誤差放大器后�,Vg增加,那么Vgs=Vg-Vs�����,Vgs也增加�,從下圖可以看到,隨著Vgs增加�����,MOS的電流Id逐漸上升,進(jìn)而使得Vout逐漸升高�����,MOS工作點(diǎn)由B轉(zhuǎn)移到C�,LDO又回到原始工作電平。

3. NMOS LDO仿真結(jié)果

下圖是簡(jiǎn)單的5V轉(zhuǎn)3.0V的NMOS LDO仿真圖以及仿真波形結(jié)果�����,橙色曲線是電壓��,綠色曲線是電流�,隨著負(fù)載端滑動(dòng)變阻器R4的變化,負(fù)載電流也在變�����,而輸出電壓基本穩(wěn)定在3.0V���。

4. LDO 輸出電容你知道多少���?

考慮到系統(tǒng)的穩(wěn)定性,LDO的輸出電容原則上是要加的��,但是如果對(duì)于成本有 的考慮,在滿足一定要求時(shí)�,這個(gè)電容其實(shí)是可以刪除的。

5. Dropout voltage

上文分析了PMOS LDO工作在恒流區(qū)(飽和區(qū))���,DS之間有一定的壓差���,此壓差常稱為dropout voltage(Vdo)����,所以LDO若想穩(wěn)定工作在飽和區(qū),輸入輸出之間滿足一定的壓差��,應(yīng)用中通??梢钥紤]在spec中預(yù)留25%的余量。比如下圖中在Iout=150mA時(shí)�,不同Vout對(duì)應(yīng)的Vdo也不同。

大電流線性電源(LDO)原理的超詳細(xì)解讀

6. 效率

效率此處不過(guò)多討論����,LDO自身消耗的功率約等于壓差*電流,因此相同負(fù)載電流下����,壓差越大�����,LDO功耗越高�,所以壓差稍微低一些���,有利于提高效率�。

7. PSRR

LDO重要參數(shù)之一也是巨大優(yōu)點(diǎn)之一便是紋波小�,即PSRR好,PSRR是電源抑制比����,是LDO對(duì)輸入電源紋波的抑制程度,PSRR的 值越大越好����。看PSRR曲線有個(gè)轉(zhuǎn)折點(diǎn)�,左邊為L(zhǎng)DO自身起主導(dǎo)作用,右邊為輸出電容起主導(dǎo)作用����,PSRR性能好的LDO左邊的曲線會(huì)更高,加大輸出電容���,右邊的曲線會(huì)升高�����。

LDO的基本原理與介紹可以告一段落了����,而其內(nèi)部實(shí)際工作情況是非常復(fù)雜的,本文只起引導(dǎo)作用���,希望能引起大家的共鳴或排解一些疑惑,歡迎關(guān)注我的公眾號(hào):硬件工程師看海�����。里面會(huì)定期更新鮮的內(nèi)容���。

(來(lái)源:硬件工程師看海)