【導讀】高速數(shù)字系統(tǒng)設計成功的關鍵在于保持信號的完整,而影響信號完整性(即信號質(zhì)量)的因素主要有傳輸線的長度、電阻匹配及電磁干擾、串擾等。

高速數(shù)字系統(tǒng)設計成功的關鍵在于保持信號的完整,而影響信號完整性(即信號質(zhì)量)的因素主要有傳輸線的長度、電阻匹配及電磁干擾、串擾等。

設計過程中要保持信號的完整性必須借助一些仿真工具,仿真結果對 PCB 布線產(chǎn)生指導性意見,布線完成后再提取網(wǎng)絡,對信號進行布線后仿真,仿真沒有問題后才能送出加工。目前這樣的仿真工具主要有 cadence、ICX、Hyperlynx 等。Hyperlynx 是個簡單好用的工具,軟件中包含兩個工具 LineSim 和 BoardSim。LineSim 用在布線設計前約束布線和各層的參數(shù)、設置時鐘的布線拓撲結構、選擇元器件的速率、診斷信號完整性,并盡量避免電磁輻射及串擾等問題。BoardSim 用于布線以后快速地分析設計中的信號完整性、電磁兼容性和串擾問題,生成串擾強度報告,區(qū)分并解決串擾問題。作者使用 LineSim 工具,對信號的阻抗匹配、傳輸線的長度、串擾進行了仿真分析,并給出了指導性結論。

阻抗匹配

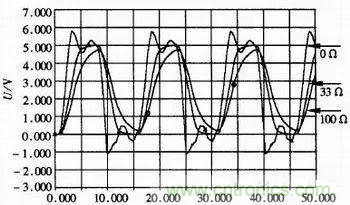

高速數(shù)字信號的阻抗匹配非常關鍵,如果匹配不好,信號會產(chǎn)生較大的上沖和下沖現(xiàn)象,如果幅度超過了數(shù)字信號的閾值,就會產(chǎn)生誤碼。阻抗匹配有串行端接和并行端接兩種,由于串行端接功耗低并且端接方便,實際工作中一般采用串行端接。以下利用 Hyperlynx 仿真工具對端接電阻的影響進行了分析。以 74 系列建立仿真 IBIS 模型如圖 1 所示。仿真時選擇一個發(fā)送端一個接收端,傳輸線為帶狀線,設置線寬 0.2mm 和介電常數(shù)為 4.5(常用的 FR4 材料),使傳輸線的阻抗為 51.7Ω。設置信號頻率為 50MHz 的方波,串行端接電阻 Rs 分別取 0Ω、33Ω和 100Ω的情況,進行仿真分析,仿真結果如圖 2 所示。

圖中分別標出了匹配電阻是 0Ω、33Ω、100Ω時接收端的信號波形。從波形看出,0Ω時波形有很大的上沖和下沖現(xiàn)象,信號最差;100Ω時信號衰減較大,方波幾乎變成了正弦波;而匹配電阻是 33Ω時波形較好。理想的匹配電阻值,可以利用軟件的 terminatorWizard 工具,自動根據(jù)器件的參數(shù)模型算出最佳匹配電阻為 33.6Ω,實際應用中可以選用 33Ω。利用仿真和器件的 IBIS 模型,可以很精確地知道匹配電阻值的大小,從而使信號完整性具有可控性。

圖 1 74 系列仿真模型

圖 2 不同串行端接電阻的仿真結果

傳輸線長度的影響

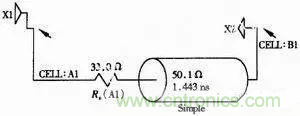

在高速數(shù)字電路的設計中,除了阻抗匹配外,部分器件對傳輸線的長度有著嚴格的要求,信號頻率越高,要求傳輸線的長度越短。以 X1 器件和 X2 器件為例建立仿真模型如圖 3 所示。在仿真模型中加了 33Ω的匹配電阻,選擇仿真信號頻率為 66MHz 方波,改變傳輸線長度分別為 76.2mm 和 254mm 時進行仿真。仿真結果如圖 4 所示。

圖 3 X1、X2 器件仿真模型

圖 4 不同長度傳輸線仿真結果

從圖中看出,信號線加長后,由于傳輸線的等效電阻、電感和電容增大,傳輸線效應明顯加強,波形出現(xiàn)振蕩現(xiàn)象。因此在高頻 PCB 布線時除了要接匹配電阻外,還應盡量縮短傳輸線的長度,保持信號完整性。

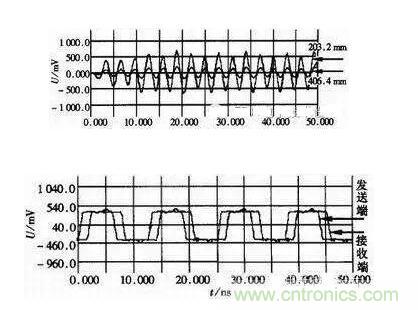

在實際的 PCB 布線時,如果由于產(chǎn)品結構的需要,不能縮短信號線長度時,應采用差分信號傳輸。差分信號有很強的抗共模干擾能力,能大大延長傳輸距離。差分信號有很多種,如 ECL、PECL、LVDS 等,表 1 列出 LVDS 相對于 ECL、PECL 系統(tǒng)的主要特點。LVDS 的恒流源模式低擺幅輸出使得 LVDS 能高速驅(qū)動,對于點到的連接,傳輸速率可達 800Mbps,同時 LVDS 低噪聲、低功耗,連接方便,實際中使用較多。LVDS 的驅(qū)動器由一個通常為 3.5mA 的恒流源驅(qū)動對差分信號線組成。接收端有一個高的直流輸入阻抗,幾科全部的驅(qū)動電流流經(jīng) 10Ω的終端電阻,在接收器輸入端產(chǎn)生約 350mV 電壓。當驅(qū)動狀態(tài)反轉(zhuǎn)時,流經(jīng)電阻的電流方向改變,此時在接收端產(chǎn)生有效的邏輯狀態(tài)。圖 5 是利用 LVDS 芯片 DS90LV031、DS90LV032 把信號轉(zhuǎn)換成差分信號,進行長距離傳輸?shù)牟ㄐ螆D。在仿真時設置仿真頻率為 66MHz 理想方波,傳輸距離為 508mm,差分對終端接 100Ω負載匹配傳輸線的差分阻抗。從仿真結果看,LVDS 接收端的波形除了有延遲外,波形保持完好。

表 1 LVDS、ECL、PECL 邏輯標準對照表

圖 5 LVDS 電路仿真結果

串擾分析

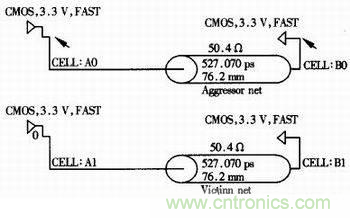

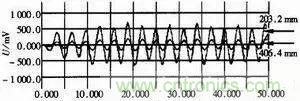

由于頻率的提高,傳輸線之間的串擾明顯增大,對信號完整性也有很大的影響,可以通過仿真來預測、模擬,并采取措施加以改善。以 CMOS 信號為例建立仿真模型,如圖 6 所示。在仿真時設置干擾信號的頻率為 66MHz 的方波,被干擾者設置為零電平輸入,通過調(diào)整兩根線的間距和兩線之間平行走線的長度來觀察被干擾者接收端的波形。仿真結果如圖 7,分別為間距是 203.2mm、406。4mm 時的波形。

圖 6 串擾模型

圖 7 不同間距的串擾仿真結果

從仿真結果看出,兩線間距為 406.4mm 時,串擾電平為 200mV 左右,203.2mm 時為 500mV 左右??梢妰删€之間的間距越小串擾越大,所以在實際高速 PCB 布線時應盡量拉大傳輸線間距或在兩線之間加地線來隔離。

結束語

在高速數(shù)字電路設計中,不用仿真而只憑傳統(tǒng)的設計方法或經(jīng)驗很難預測和保證信號完整性,仿真已成為高速信號設計的必要手段,利用仿真可以預測信號的傳輸情況,從而提高系統(tǒng)的可靠性。

免責聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯(lián)系小編進行處理。